Section 2 introduces the instr, 2 instruction cache – Motorola DSP96002 User Manual

Page 785

MOTOROLA

3

stated during hardware reset, requires a weak external pull-up resistor, and can be con-

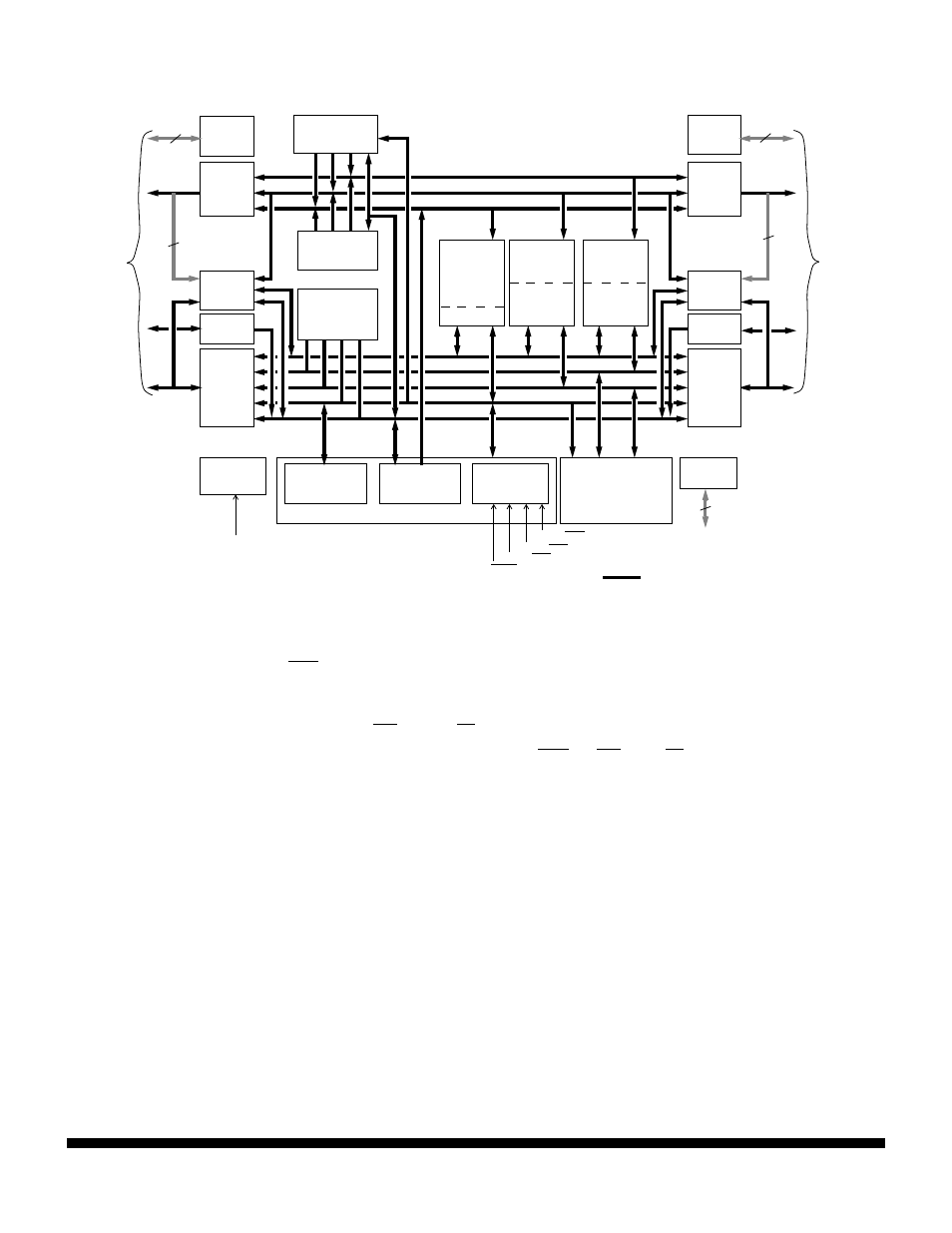

nected directly to the WE pin of a static RAM. The DSP96002 diagram shown in Figure 6

on page 29 includes the new write strobe pins.

The timings and functionality of TS and R/W remain unchanged, so that existing configu-

rations may still be used. From a logical standpoint, WR = (TS or R/W).

2 INSTRUCTION CACHE

2.1

INTRODUCTION

The instruction cache may be viewed as a buffer memory between the main (external

and probably slow) memory, and the fast CPU. The cache is used to store frequently

used program instructions and it offers an increase in throughput by eliminating the time

required to access the instruction words on the external bus.

Reduced external bus activity maintains single-cycle program memory access, while al-

lowing the use of a low cost, slow external program memory. It also frees the processor’s

memory expansion port for other tasks such as data moves, DMA transfers, Host Interface

data moves, etc.

Figure 1 - DSP96002 Block Diagram

INTERNAL

SWITCH and BIT

MANIPULATION

UNIT

PROGRAM CONTROLLER

ADDRESS

DATA

YAB

XAB

PAB

YDB

XDB

PDB

GDB

32-BIT HOST

INTERFACE

PROGRAM

ADDRESS

GENERATOR

PROGRAM

ADDRESS

GENERATOR

PROGRAM

INTERRUPT

CONTROLLER

CLOCK

GENERATOR

DDB

DUAL CHANNEL

DMA

CONTROLLER

OnCE DEBUG

CONTROLLER

4

SERIAL

DEBUG

PORT

MODB/IRQB

MODA/IRQA

RESET

EXTERNAL

ADDRESS

SWITCH

ADDRESS

GENERATION

UNIT (AGU)

EXTERNAL

DATA BUS

SWITCH

• IEEE FLOATING POINT

• 32x32 INTEGER ALU

CLK

MEMORY

512x32

RAM

MEMORY

512x32

RAM

PROGRAM

1024x32

RAM

and

64x32

BOOTSTRAP

ROM

512x32

ROM

512x32

ROM

DATA ALU

32-BIT BUSES

ADDRESS

EXTERNAL

ADDRESS

SWITCH

BUS

CONTROL

CONTROL

EXTERNAL

DATA BUS

SWITCH

PORT B

MEMORY

X DATA

Y DATA

32

MODC/IRQC

BUS

CONTROL

CONTROL

32-BIT HOST

INTERFACE

DATA

32

*

*

*

*

*

*

*

DUAL ACCESS (DMA/CORE)

4

4

19

19

INSTRUCTION

CACHE

TIMER

TIMER

PORT A