Motorola DSP96002 User Manual

Page 818

36

MOTOROLA

Note: It is recommended that the GPIO input function of Mode 0 only be activated with

the timer disabled. If the processor attempts to read the DI bit, it must read the entire

TCSR register, which would clear the TS bit and, thus, clear a pending timer interrupt.

6.4.2

Timer Mode 1 (Standard Timer Mode, Internal Clock, Output Pulse Enabled)

Timer Mode 1 is defined by TC2-TC0 equal to 001.

With the timer enabled (TE=1), the counter is loaded with the value contained by the TCR.

The counter is decremented by a clock derived from the DSP’s internal clock, divided by

two (CLK/2). During the clock cycle following the point where the counter reaches 0, the

TS bit is set and the timer generates an interrupt. A pulse with a width equal to two clock

cycles, and whose polarity is determined by the INV bit, will be put out on the TIO pin. The

counter is reloaded with the value contained by the TCR and the entire process is repeat-

ed until the timer is disabled (TE=0). Figure 11 illustrates Timer Mode 1 when INV=0, and

Figure 12 illustrates Timer Mode 1 when INV=1.

6.4.3 Timer Mode 2 (Standard Timer Mode, Internal Clock, Output Toggle Enabled)

Timer Mode 2 is defined by TC2-TC0 equal to 010.

With the timer enabled (TE=1), the counter is loaded with the value contained by the TCR.

The counter is decremented by a clock derived from the DSP’s internal clock, divided by

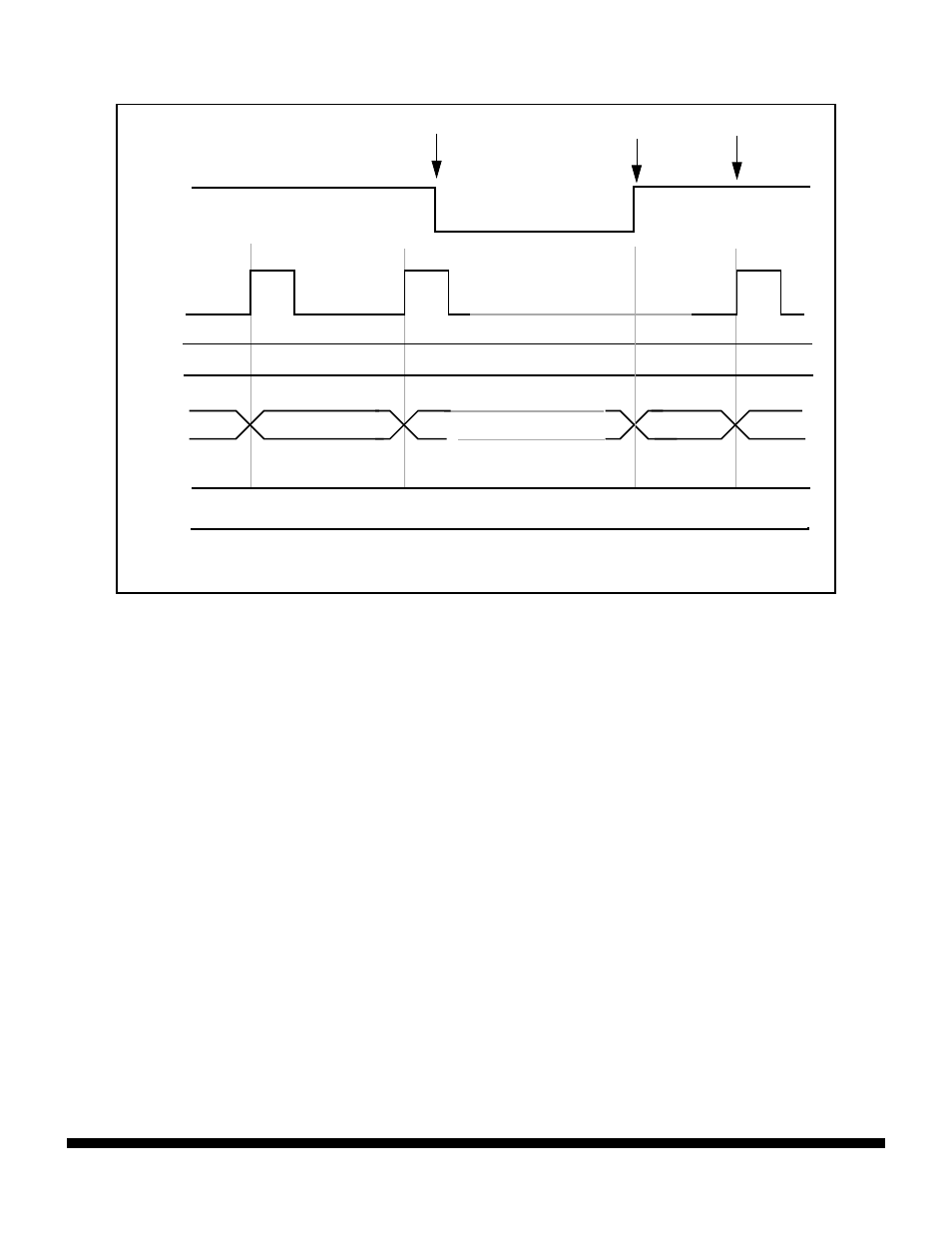

TE

TCR

N

Counter

N-k

N-k-1

N

TS

first event

N-k-1

stop

N-1

Clock

Interrupt

Figure 10 - Timer Disabled

write to

TCR (N)

counting

(CLK/2)