Motorola DSP96002 User Manual

Page 787

MOTOROLA

5

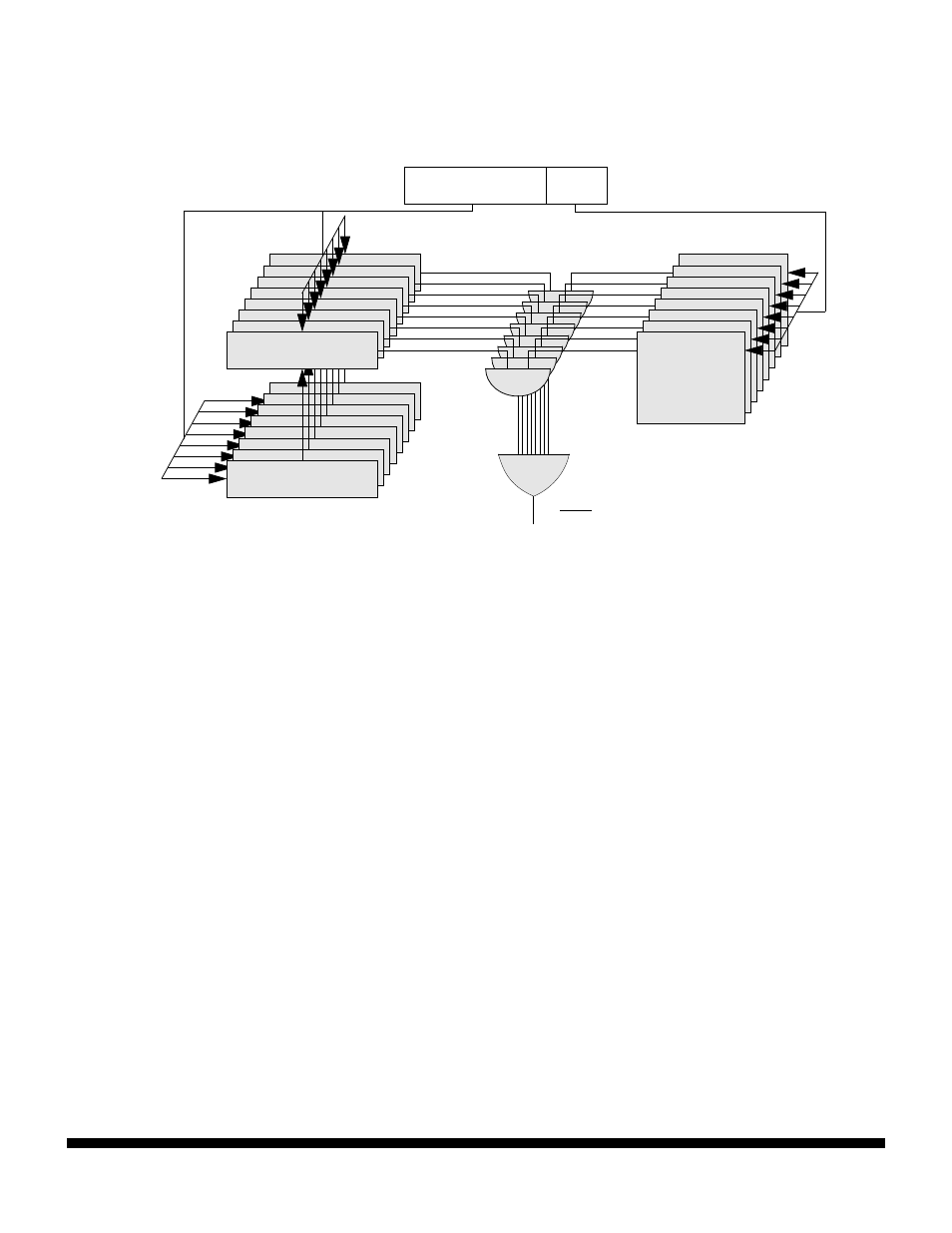

Since there are 8 sectors of 128 words each, in the internal program RAM, the 32 bit ad-

dress is divided into the following two fields:

• 7 LSBs for the word displacement or offset in the sector

• 25 MSBs for the tag

The sector placement algorithm is fully associative so that each external program memory

sector could be placed in any of the 8 internal program RAM sectors, essentially making

it an eight-way fully associative cache.

A 25-bit tag is associated with every one of the eight internal program memory RAM sec-

tors. When the cache controller searches for a tag equal to the tag field of the current ad-

dress, it compares it to the eight tags in parallel using the eight comparators.

Each word in each cache sector is associated with a cache-word-valid-bit (or valid-bit),

that specifies whether the data in that word has already been fetched from external mem-

ory and is therefore valid. There are a total of 1024 valid-bits, arranged as eight banks of

128 valid-bits each, one bank for every sector. Note that the valid-bits are not available to

the user for direct use. They are cleared by the processor RESET to indicate that the

PRAM context has not been initialized.

32 bit address

25 bit Tag Field

7 bits

comparator 0

tag 0

128 valid

bits for

sector 0

hit/miss

Figure 2 - Cache Controller Block Diagram

Tag Values