Motorola DSP96002 User Manual

Page 152

8 - 12

DSP96002 USER’S MANUAL

MOTOROLA

8.5.2 Interrupt Priority Register (IPR)

This read/write register specifies the interrupt priority level for each of the interrupting devices (Host, DMA,

IRQA, IRQB, IRQC). In addition, this register specifies the trigger mode of each external interrupt source

and shows the status of the external interrupt request. The register is cleared on Hardware reset or by the

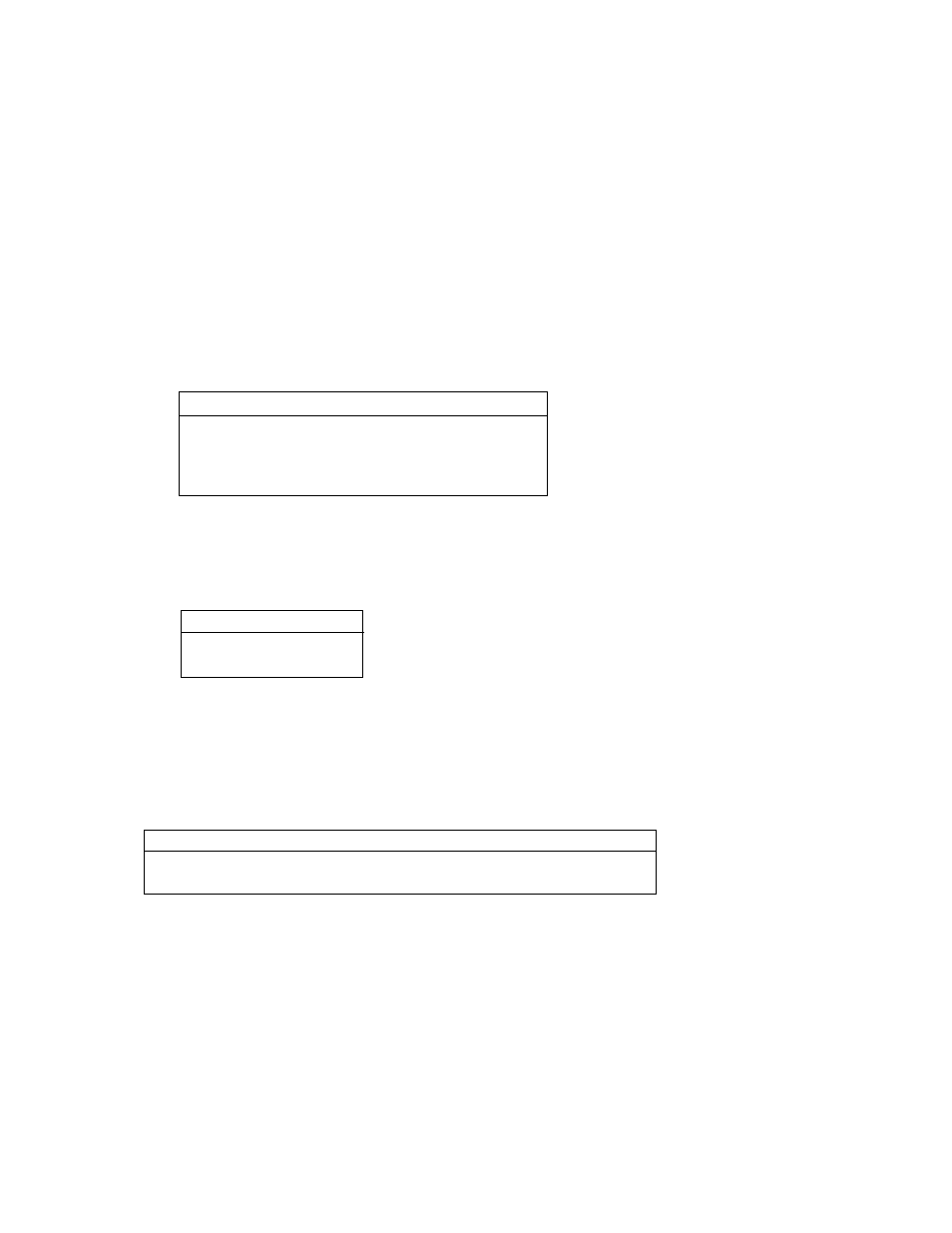

RESET instruction. The Interrupt Priority Register is shown in Figure 8-9. Figure 8-10 defines the interrupt

priority level bits. Figure 8-11 defines the external interrupt trigger mode bits and status information.

8.5.2.1 IRQA Interrupt Priority Level - IAL1-IAL0 (Bits 0-1)

The IRQA Interrupt Priority Level (IAL1-IAL0) bits are used to enable and specify the priority level of the

external interrupt input IRQA.

8.5.2.2

IRQA Trigger Mode - IAL2 (Bit 2)

The IRQA Trigger Mode (IAL2) bit specifies the trigger method for the external interrupt input IRQA.

8.5.2.3

IRQA Status - IRAS (Bit 3)

The read-only IRQA Status (IRAS) bit indicates the status of the interrupt request for the external interrupt

input IRQA. If the IRQA interrupt is defined as edge-sensitive and it is enabled, the IRAS bit indicates

the state of the edge-detection latch. If the IRQA interrupt is defined as level-sensitive or is disabled,

the IRAS bit indicates the state of the IRQA pin after internal synchronization.

8.5.2.4

IRQB Interrupt Priority Level - IBL1-IBL0 (Bits 4-5)

The IRQB Interrupt Priority Level (IBL1-IBL0) bits are used to enable and specify the priority level of the

external interrupt input IRQB.

IAL1 IAL0 Enabled Int. Priority Level (IPL)

0

0

no

-

0

1

yes

0

1

0

yes

1

1

1

yes

2

IAL2 Trigger Mode

0

level

1

negative edge

IRAS Status (edge and enabled) IRQA pin (level or disabled)

0

Serviced

High

1

Pending

Low