Motorola DSP96002 User Manual

Page 168

10 - 2

DSP96002 USER’S MANUAL

MOTOROLA

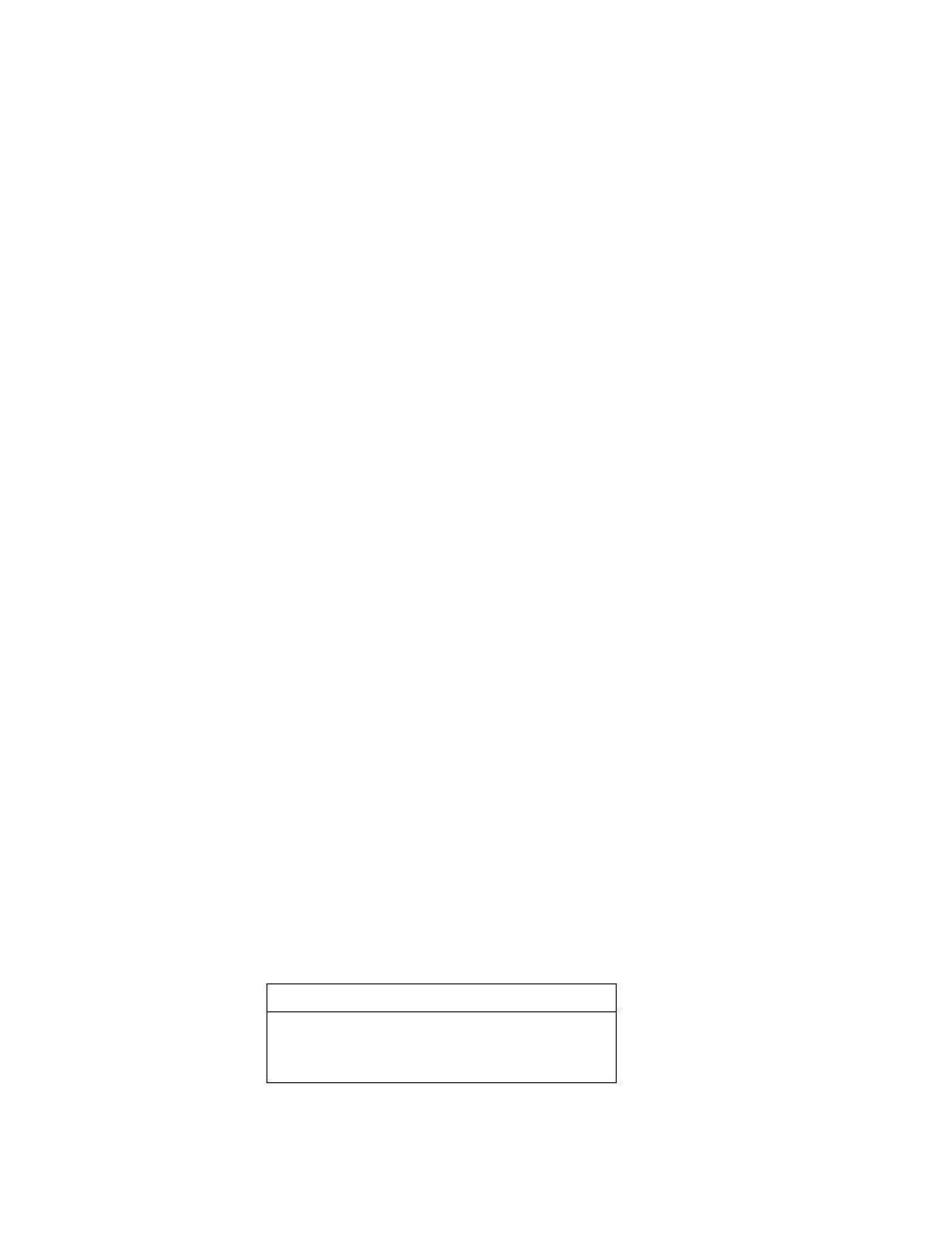

Figure 10-1. OnCE

Block Diagram

10.2.2

Debug Serial Clock/Chip Status 1 (DSCK/OS1)

The serial clock is supplied to the OnCE

through the DSCK/OS1 pin when it is an input. The serial clock

provides pulses required to shift data into and out of the OnCE

serial port. Data is clocked into the OnCE

on the falling edge and is clocked out of the OnCE

serial port on the rising edge. When an output, this pin

in conjunction with the OS0 pin, provides information about the chip status describing why the debug mode

cannot be entered in response to an external request. The DSCK/OS1 pin is output when not in the Debug

Mode (until the acknowledge signal is issued to the Command Controller). When switching from output to

input, the pin is three-stated. In order to avoid any possible glitches, an external pull-down resistor should

be attached to this pin. During hardware reset, this pin is defined as an output and it is driven low. The max-

imum SCK frequency is one third of the system clock frequency.

OS1 OS0 Status

0 0 Normal state

0 1 STOP or WAIT state

1 0 Core busy state

1 1 Core or DMA busy state