Peripheral hardware functions, Toshiba – Toshiba TMP87CP24AF User Manual

Page 52

Attention! The text in this document has been recognized automatically. To view the original document, you can use the "Original mode".

TOSHIBA

TMP87CM24A/P24A

2. Peripheral Hardware Functions

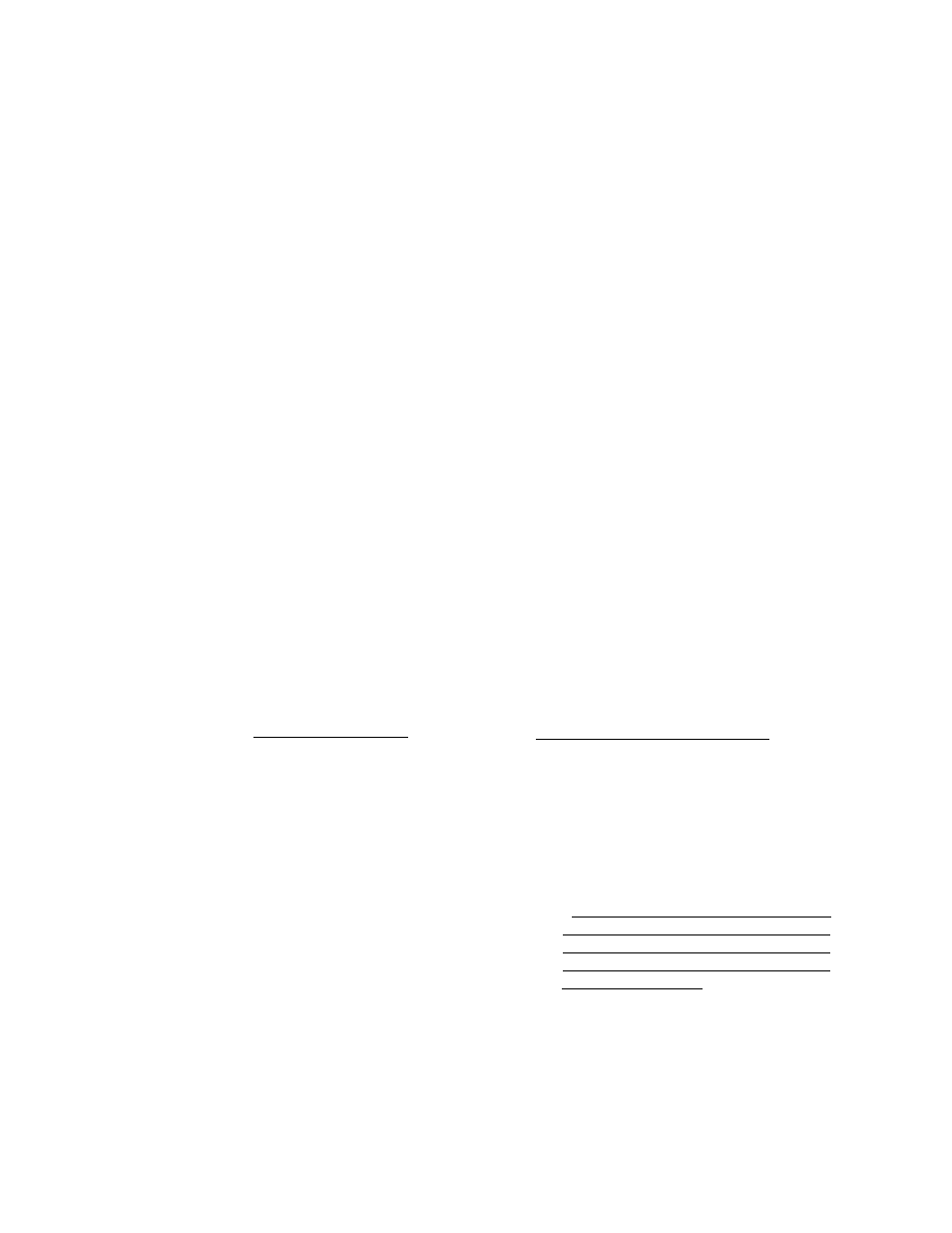

2.1 Special Function Registers (SFR) and Data Buffer Registers (DBR)

The

TLCS-870

Series

uses

the

memory

mapped

I/O

system,

and

all

peripherals

control

and

data

transfers

are performed through the special function registers (SFR) and data buffer registers (DBR).

The SFR are mapped to addresses OOOO

h

to OOBF

h

and the DBR to addresses OFBO

h

to OFFF

h

-

Figure 2-1 shows the TMP87CM24A/P24A SFRs and DBRs.

Address

OOOO

h

01

02

03

04

05

06

07

08

09

OA

OB

OC

OD

OE

OF

10

11

12

13

14

15

16

17

18

19

1A

IB

1C

ID

IE

IF

Address

0F80

h

0F93

0F94

OFEF

OFFO

0FF7

0FF8

OFFF

Read

Write

PO Port

PI Port

P2 Port

P3 Port

P4 Port

P5 Port

P6 Port

P7 Port

P8 Port

P9 Port

POCR (PO I/O control)

P1CR(P1 I/O control)

P4CR1 (P4 I/O control)

P5CR (P5 I/O control)

ADCCR (AD converter control)

ADCDR (AD conv. result)

TREGIA

l

TREGIA

h

(Timer register 1A)

TREG1B,

TREGIB

h

■■ (Timer register 1B)

TCI CR (TCI control)

TC2CR (TC2 control)

TREG2,

TREG2.

(Timer register 2)

TREG3A (Timer register 3A)

TREG3B (Timer register 3B)

TC3CR (TC 3 control)

reserved

reserved

TREG5 (Timer registers)

TC5CR (TC 5 control)

EINT3CR (External interrupt control 2)

Address

0020

h

21

22

23

24

25

26

27

28

29

2A

2B

2C

2D

2E

2F

30

31

32

33

34

35

36

37

38

39

3A

3B

3C

3D

3E

3F

Read

Write

SI01SR(SI01 status)

SI01CR1

SI02SR(SI02 status)

SI01CR2

(SI01 control)

SI02CR1

SI02CR2

(SI02 control)

Reserved

Reserved

Reserved

Reserved

LCDCR (LCD control)

•P 7.C P. i P./ .^9 9 P? .9 9.9 i 9 9^. 99 P.^. (9J}

P8CR (pSsegpieptgutput control)

P9CR (pSsegpieptgutput control)

P4CR2 (P4 output control)

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

yVDJCRI

WDTCR2

•(

WDT

control

TBTCR (TBT^G/pyO

control)

EINTCR

(External Interrupt control l)

SYSCR1

SYSCR2

EIR,

EIR

■ (System control).......................

■ (Interrupt enable register)--

■■ (Interrupt latch)-

Reserved

PSW (program status word)

I

RBS (register bank selector)

(a) Special Function Registers

Read

Write

LCD

display data buffer

Reserved

5101

transmit and receive

data buffer

5102

transmit and receive

data buffer

Note 1: Do not access reserved areas by the program.

Note

2:

When

defining

address

003F

h

with

assembler

symbols, use GPSW and GRBS.

Note3:

Do not access.

Note

4:

Operations

specified

to

writing

registers

and

interrupt

latches

by

read

modifying

write

instructions

(bit

operation

instructions

such

as

SET, CLR, etc. , or operation instructions such as

AND, OR, etc.) are not effective.

(b) Data Buffer Registers

Figure 2-1. SFR & DBR

3

-

24-52

2002

-

10-03