S:26-s:35 – Rockwell Automation 1785-Lx0C15 ControlNet PLC-5 Programmable Controllers User Manual User Manual

Page 112

1785-UM022C-EN-P - February 2008

B-12

Processor Status File

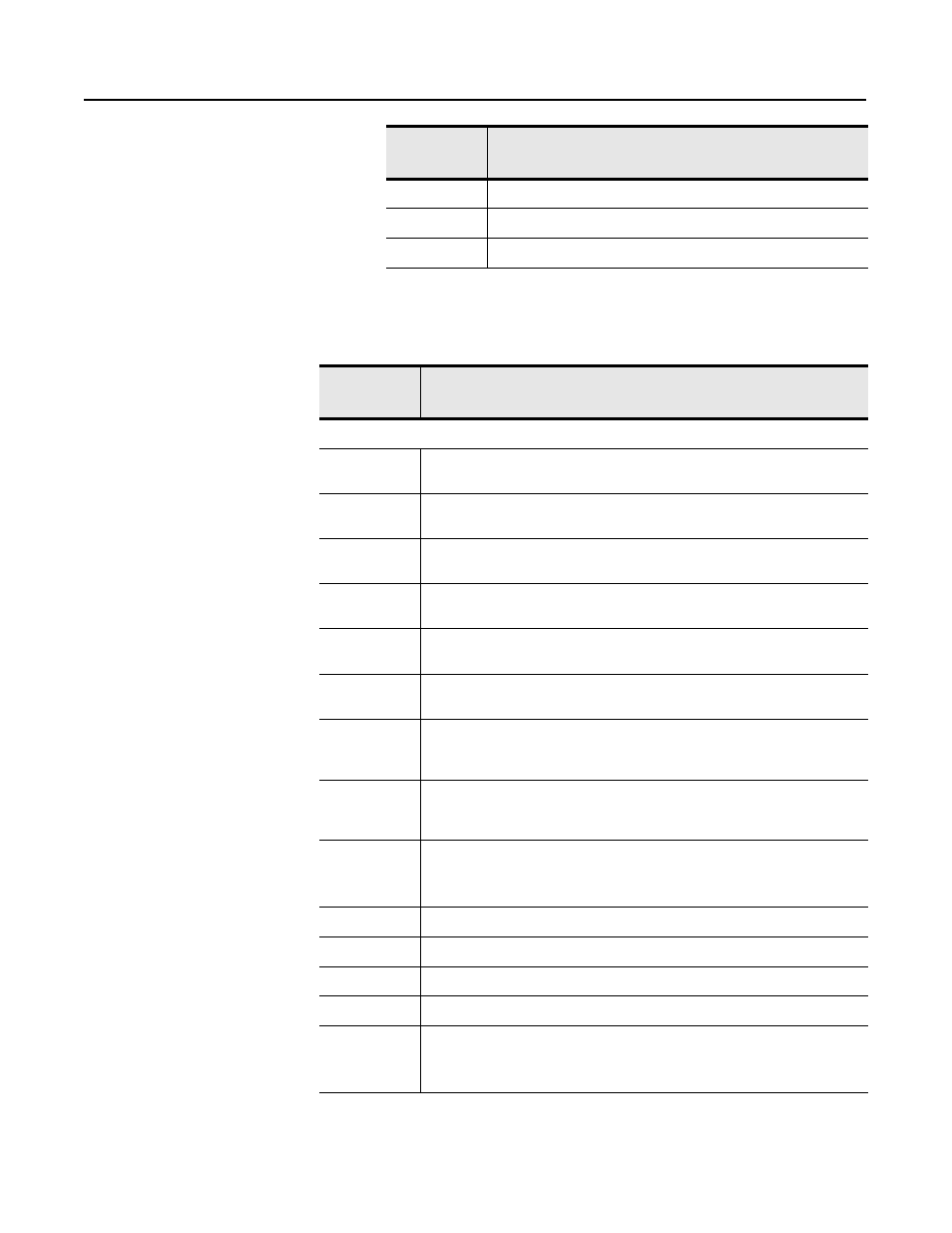

S:26-S:35

S:23

Processor clock second

S:24

Indexed addressing offset

S:25

Reserved

This word of

the status file:

Stores:

This word of

the status file:

Stores:

S:26

User control bits

S:26/00

Restart/continuous SFC: when reset, processor restarts at first step in SFC. When

set, processor continues with active step after power loss or change to RUN

S:26/01

Start-up protection after power loss: when reset, no protection. When set,

processor sets major fault bit S:11/5 when powering up in run mode.

S:26/02

Define the address of the local rack: when reset, local rack address is 0. When set,

local rack address is 1.

S:26/03

Set complementary I/O (series A only): when reset, complementary I/O is not

enabled. When set, complementary I/O is enabled.

S:26/04

Local block-transfer compatibility bit: when reset, normal operation. When set,

eliminates frequent checksum errors to certain BT modules.

S:26/05

PLC-3 scanner compatibility bit: when set (1), adapter channel response delayed by

1 ms; when reset (0) operate in normal response time.

S:26/06

Data table-modification inhibit bit. When set (1), user cannot edit the data table or

modify forces while the processor keyswitch is in the RUN position. You control this

bit with your programming software

S:26/07

through

S:26/15

Reserved

S:27

Rack control bits: (See also S:7, S:32, S:33, S:34, and S:35)

• S:27/0-7 - - I/O rack inhibit bits for racks 0-7

• S:27/8-15 - - I/O rack reset bits for racks 0-7

S:28

Program watchdog setpoint

S:29

Fault routine file

S:30

STI setpoint

S:31

STI file number

S:32

Global status bits: (See also S:7, S:27, S:33, S:34, and S:35)

• S:32/0-7

rack fault bits for racks 10-17 (octal)

• S:32/8-15

unused