2 logical device control and configuration, 1 ldn 00h - real-time clock, Table 5-6 – AMD Geode SC2200 User Manual

Page 98: Relevant rtc configuration registers

104

AMD Geode™ SC2200 Processor Data Book

SuperI/O Module

32580B

5.4.2

Logical Device Control and

Configuration

As described in Section 5.3.2 "Banked Logical Device Reg-

isters" on page 98, each functional block is associated with

a Logical Device Number (LDN). This section provides the

register descriptions for each LDN.

The register descriptions in this subsection use the follow-

ing abbreviations for Type:

• R/W

= Read/Write

• R

= Read from a specific address returns the

value of a specific register. Write to the

same address is to a different register.

• W

= Write

• RO

= Read Only

• R/W1C = Read/Write 1 to Clear. Writing 1 to a bit

clears it to 0. Writing 0 has no effect.

5.4.2.1

LDN 00h - Real-Time Clock

Table 5-6 lists the registers which are relevant to configura-

tion of the Real-Time Clock (RTC). Only the last registers

(F0h-F3h) are described here (Table 5-7). See Table 5-3

"Standard Configuration Registers" on page 101 for

descriptions of the other registers.

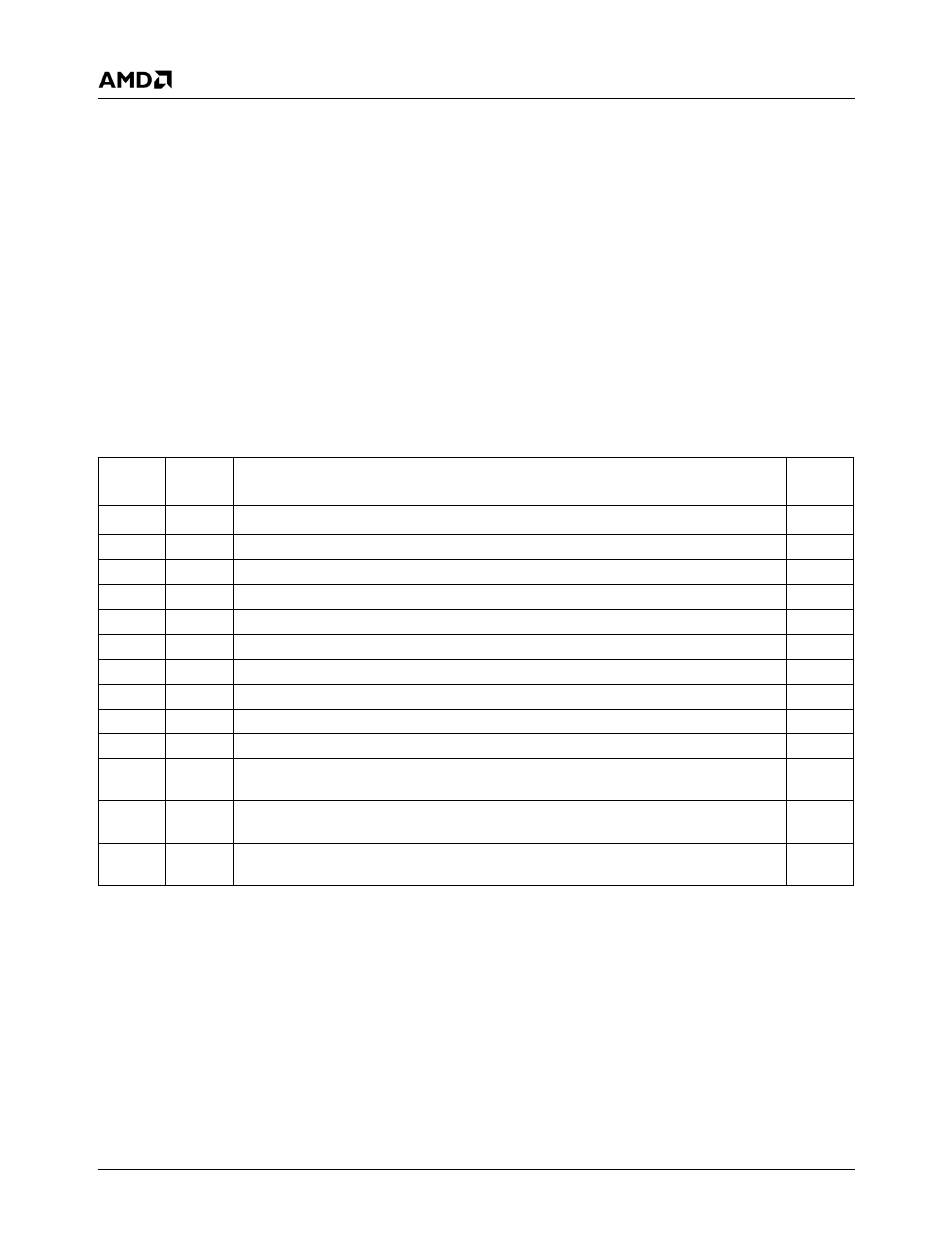

Table 5-6. Relevant RTC Configuration Registers

Index

Type

Configuration Register or Action

Reset

Value

30h

R/W

Activate. When bit 0 is cleared, the registers of this logical device are not accessible.

1

00h

60h

R/W

Standard Base Address MSB register. Bits [7:3] (for A[15:11]) are RO, 00000b.

00h

61h

R/W

Standard Base Address LSB register. Bit 0 (for A0) is RO, 0b.

70h

62h

R/W

Extended Base Address MSB register. Bits [7:3] (for A[15:11]) are RO, 00000b.

00h

63h

R/W

Extended Base Address LSB register. Bit 0 (for A0) is RO, 0b.

72h

70h

R/W

Interrupt Number. 08h

71h

R/W

Interrupt Type. Bit 1 is R/W; other bits are RO.

00h

74h

RO

Report no DMA assignment. 04h

75h

RO

Report no DMA assignment. 04h

F0h

R/W

RAM Lock register (RLR). 00h

F1h

R/W

Date of Month Alarm Offset register (DOMAO). Sets index of Date of Month Alarm

register in the standard base address.

00h

F2h

R/W

Month Alarm Offset register (MONAO). Sets index of Month Alarm register in the

standard base address.

00h

F3h

R/W

Century Offset register (CENO). Sets index of Century register in the standard base

address.

00h

1.

The logical device registers are maintained, and all RTC mechanisms are functional.