AMD Geode SC2200 User Manual

Page 35

AMD Geode™ SC2200 Processor Data Book

35

32580B

T30

V

CORE

PWR

---

---

---

T31

V

CORE

PWR

---

---

---

U1

AD0

I/O

IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

A0

O

O

PCI

U2

IDE_ADDR2

O

O

1/4

V

IO

PMR[24] = 0

TFTD4

O

O

1/4

PMR[24] = 1

U3

AD2

I/O

IN

PCI

,

O

PCI

V

IO

Cycle Multiplexed

A2

O

O

PCI

U4

V

CORE

PWR

---

---

---

U13

V

SS

GND

---

---

---

U14

V

SS

GND

---

---

---

U15

V

SS

GND

---

---

---

U16

V

SS

GND

---

---

---

U17

V

SS

GND

---

---

---

U18

V

SS

GND

---

---

---

U19

V

SS

GND

---

---

---

U28

V

CORE

PWR

---

---

---

U29

AC97_RST#

O

O

2/5

V

IO

FPCI_MON = 0

F_STOP#

O

O

2/5

FPCI_MON = 1

U30

BIT_CLK

I

IN

T

V

IO

FPCI_MON = 0

F_TRDY#

O

O

1/4

FPCI_MON = 1

U31

SDATA_IN

I

IN

T

V

IO

FPCI_MON = 0

F_GNT0#

O

O

2/5

FPCI_MON = 1

V1

IDE_DATA15

I/O

IN

TS1

,

TS

1/4

V

IO

PMR[24] = 0

TFTD7

O

O

1/4

PMR[24] = 1

V2

IDE_DATA14

I/O

IN

TS1

,

TS

1/4

V

IO

PMR[24] = 0

TFTD17

O

O

1/4

PMR[24] = 1

V3

IDE_DATA13

I/O

IN

TS1

,

TS

1/4

V

IO

PMR[24] = 0

TFTD15

O

O

1/4

PMR[24] = 1

V4

V

SS

GND

---

---

---

V13

V

CORE

PWR

---

---

---

V14

V

CORE

PWR

---

---

---

V15

V

SS

GND

---

---

---

V16

V

SS

GND

---

---

---

V17

V

SS

GND

---

---

---

V18

V

CORE

PWR

---

---

---

V19

V

CORE

PWR

---

---

---

V28

V

SS

GND

---

---

---

V29

SDCLK3

O

O

2/5

V

IO

---

V30

GXCLK

O

O

2/5

V

IO

PMR[23]

3

= 0 and

PMR[29] = 0

FP_VDD_ON

O

O

1/4

PMR[23]

3

= 1

TEST3

O

O

2/5

PMR[23]

3

= 0 and

PMR[29] = 1

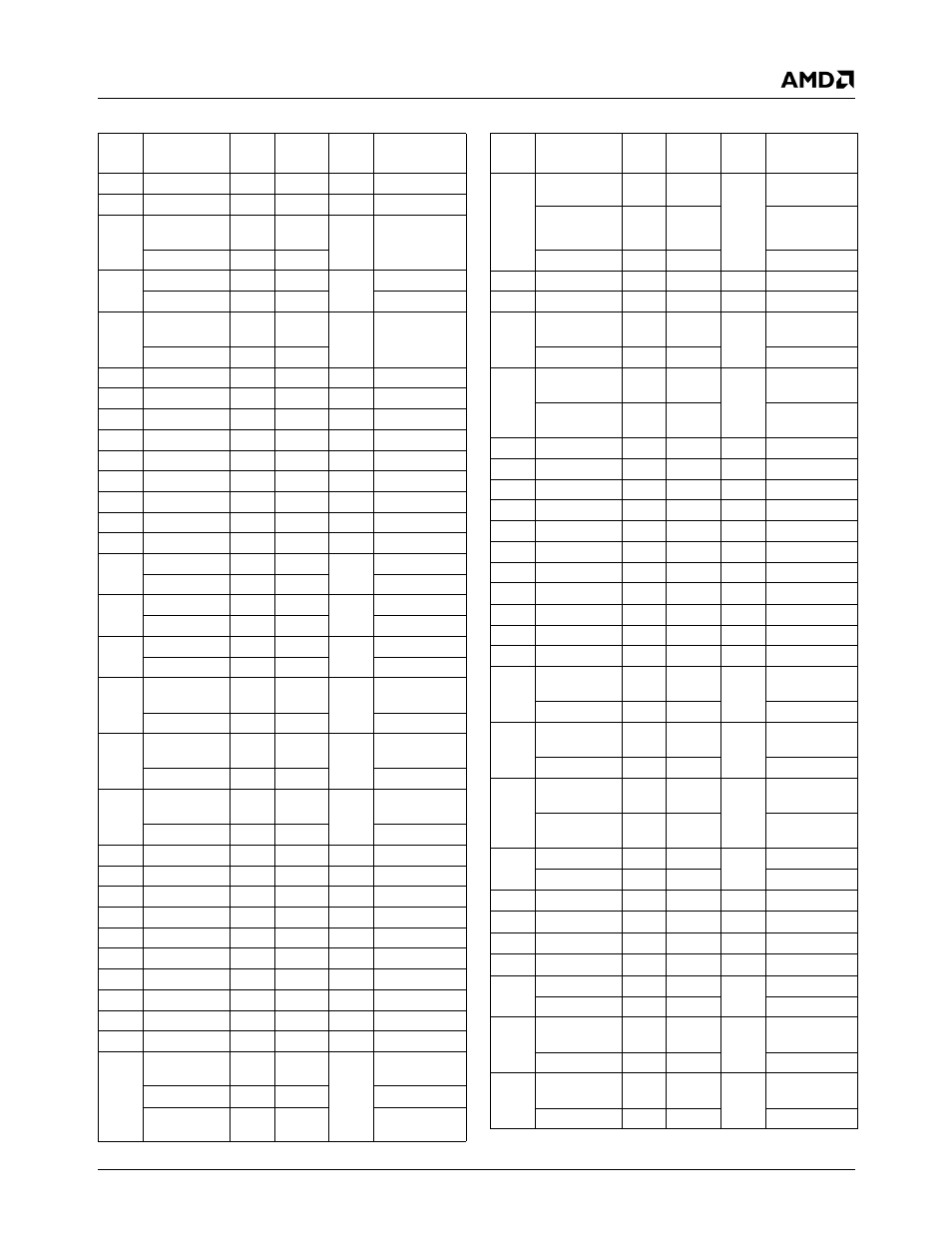

Ball

No.

Signal Name

I/O

(PU/PD)

Buffer

1

Type

Power

Rail

Configuration

V31

GPIO16

I/O

(PU

22.5

)

IN

T

, O

2/5

V

IO

PMR[0] = 0 and

FPCI_MON = 0

PC_BEEP

O

O

2/5

PMR[0] = 1 = 0

and FPCI_MON =

0

F_DEVSEL#

O

O

2/5

FPCI_MON = 1

W1

V

IO

PWR

---

---

---

W2

V

SS

GND

---

---

---

W3

IDE_DATA12

I/O

IN

TS1

,

TS

1/4

V

IO

PMR[24] = 0

TFTD13

O

O

1/4

PMR[24] = 1

W4

IDE_DATA11

I/O

IN

TS1

,

TS

1/4

V

IO

PMR[24] = 0

GPIO41

I/O

IN

TS1

,

O

1/4

PMR[24] = 1

W13

V

CORE

PWR

---

---

---

W14

V

CORE

PWR

---

---

---

W15

V

SS

GND

---

---

---

W16

V

SS

GND

---

---

---

W17

V

SS

GND

---

---

---

W18

V

CORE

PWR

---

---

---

W19

V

CORE

PWR

---

---

---

W28

6

MD57

I/O

IN

T

, TS

2/5

V

IO

---

W29

SDCLK1

O

O

2/5

V

IO

---

W30

V

SS

GND

---

---

---

W31

V

IO

PWR

---

---

---

Y1

5

IDE_DATA10

I/O

IN

TS1

,

TS

1/4

V

IO

PMR[24] = 0

DDC_SCL

O

OD

4

PMR[24] = 1

Y2

5

IDE_DATA9

I/O

IN

TS1

,

TS

1/4

V

IO

PMR[24] = 0

DDC_SDA

I/O

IN

T

, OD

4

PMR[24] = 1

Y3

IDE_DATA8

I/O

IN

TS1

,

TS

1/4

V

IO

PMR[24] = 0

GPIO40

I/O

IN

TS1

,

O

1/4

PMR[24] = 1

Y4

IDE_IOR0#

O

O

1/4

V

IO

PMR[24] = 0

TFTD10

O

O

1/4

PMR[24] = 1

Y28

6

MD58

I/O

IN

T

, TS

2/5

V

IO

---

Y29

6

MD59

I/O

IN

T

, TS

2/5

V

IO

---

Y30

6

MD60

I/O

IN

T

, TS

2/5

V

IO

---

Y31

6

MD56

I/O

IN

T

, TS

2/5

V

IO

---

AA1

IDE_RST#

O

O

1/4

V

IO

PMR[24] = 0

TFTDCK

O

O

1/4

PMR[24] = 1

AA2

IDE_DATA7

I/O

IN

TS1

,

TS

1/4

V

IO

PMR[24] = 0

INTD#

I

IN

TS

PMR[24] = 1

AA3

IDE_DATA6

I/O

IN

TS1

,

TS

1/4

V

IO

PMR[24] = 0

IRQ9

I

IN

TS1

PMR[24] = 1

Ball

No.

Signal Name

I/O

(PU/PD)

Buffer

1

Type

Power

Rail

Configuration

Table 3-2. BGU481 Ball Assignment - Sorted by Ball Number (Continued)