AMD Geode SC2200 User Manual

Page 38

38

AMD Geode™ SC2200 Processor Data Book

32580B

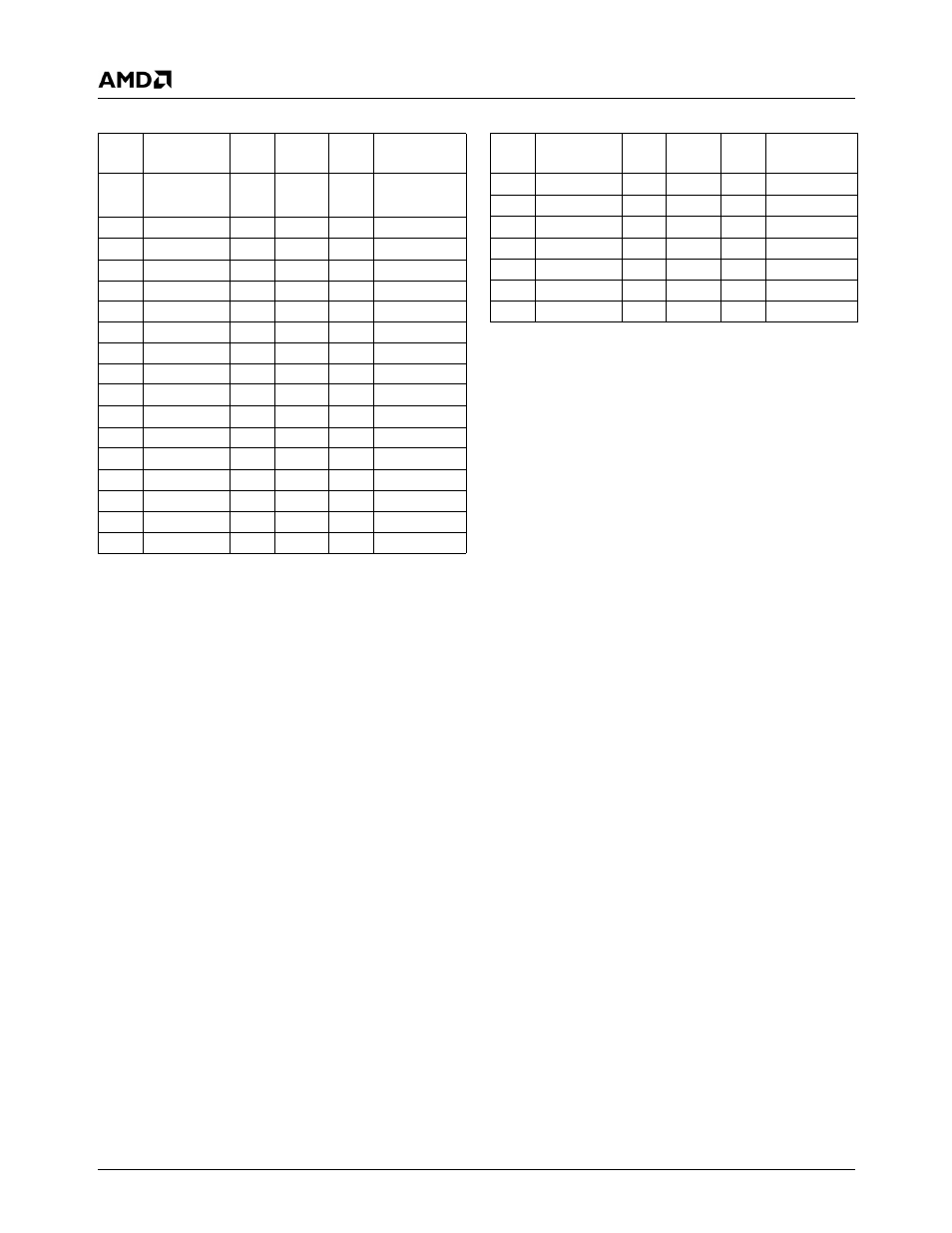

AL8

SDATA_IN2

I

IN

TS

V

SB

F3BAR0+Mem-

ory Offset 08h[21]

= 1

AL9

6

MD2

I/O

IN

T

, TS

2/5

V

IO

---

AL10

6

MD4

I/O

IN

T

, TS

2/5

V

IO

---

AL11

DQM0

O

O

2/5

V

IO

---

AL12

CS0#

O

O

2/5

V

IO

---

AL13

V

SS

GND

---

---

---

AL14

MA0

O

O

2/5

V

IO

---

AL15

DQM4

O

O

2/5

V

IO

---

AL16

V

SS

GND

---

---

---

AL17

6

MD38

I/O

IN

T

, TS

2/5

V

IO

---

AL18

6

MD39

I/O

IN

T

, TS

2/5

V

IO

---

AL19

V

SS

GND

---

---

---

AL20

6

MD44

I/O

IN

T

, TS

2/5

V

IO

---

AL21

6

MD40

I/O

IN

T

, TS

2/5

V

IO

---

AL22

CKEA

O

O

2/5

V

IO

---

AL23

MA7

O

O

2/5

V

IO

---

AL24

MA4

O

O

2/5

V

IO

---

Ball

No.

Signal Name

I/O

(PU/PD)

Buffer

1

Type

Power

Rail

Configuration

AL25

6

MD8

I/O

IN

T

, TS

2/5

V

IO

---

AL26

6

MD10

I/O

IN

T

, TS

2/5

V

IO

---

AL27

6

MD9

I/O

IN

T

, TS

2/5

V

IO

---

AL28

MA12

O

O

2/5

V

IO

---

AL29

6

MD23

I/O

IN

T

, TS

2/5

V

IO

---

AL30

V

IO

PWR

---

---

---

AL31

V

SS

GND

---

---

---

1.

For Buffer Type definitions, refer to Table 9-10 "Buffer Types" on page

376.

2.

Is 5V tolerant (ACK#, AFD#/DSTRB#, BUSY/WAIT#, ERR#, INIT#,

PD[7:0], PE, SLCT, SLIN#/ASTRB#, STB#/WRITE#, ONCTL#,

PWRCNT[2:1]).

3.

The TFT_PRSNT strap determines the power-on reset (POR) state of

PMR[23].

4.

The LPC_ROM strap determines the power-on reset (POR) state of

PMR[14] and PMR[22].

5.

May need 5V tolerant protection at system level (DDC_SCL,

DDC_SDA).

6.

Is back-drive protected (MD[63:0], DPOS_PORT1, DNEG_PORT1,

DPOS_PORT2, DNEG_PORT2, DPOS_PORT3, DNEG_PORT3,

ACK#, AFD#/DSTRB#, BUSY/WAIT#, ERR#, INIT#, PD[7:0], PE, SLCT,

SLIN#/ASTRB#, STB#/WRITE#, ONCTL#, PWRCNT[2:1]).

Ball

No.

Signal Name

I/O

(PU/PD)

Buffer

1

Type

Power

Rail

Configuration

Table 3-2. BGU481 Ball Assignment - Sorted by Ball Number (Continued)