AMD Geode SC2200 User Manual

Page 205

AMD Geode™ SC2200 Processor Data Book

213

Core Logic Module - Bridge, GPIO, and LPC Registers - Function 0

32580B

2

Parallel/Serial Access Trap.

0: Disable.

1: Enable.

If this bit is enabled and an access occurs in the address ranges listed below, an SMI is generated.

— LPT1: I/O Port 3BCh-3BEh.

— LPT2: I/O Port 378h-37Fh.

— COM1: I/O Port 3F8h-3FFh (if F0 Index 93h[1:0] = 10 this range is excluded).

— COM2: I/O Port 2F8h-2FFh (if F0 Index 93h[1:0] = 11 this range is excluded).

— COM3: I/O Port 3E8h-3EFh.

— COM4: I/O Port 2E8h-2EFh.

Top level SMI status is reported at F1BAR0+I/O Offset 00h/02h[0].

Second level SMI status is reported at F0 Index 86h/F6h[2].

1

Floppy Disk Access Trap.

0: Disable.

1: Enable.

If this bit is enabled and an access occurs in the address ranges listed below, an SMI is generated.

— Primary floppy disk: I/O Port 3F2h-3F5h, 3F7h.

— Secondary floppy disk: I/O Port 372h-375h, 377h.

Top level SMI status is reported at F1BAR0+I/O Offset 00h/02h[0].

Second level SMI status is reported at F0 Index 86h/F6h[1].

0

Primary Hard Disk Access Trap.

0: Disable.

1: Enable.

If this bit is enabled and an access occurs in the address ranges selected in F0 Index 93h[5], an SMI is generated.

Top level SMI status is reported at F1BAR0+I/O Offset 00h/02h[0].

Second level SMI status is reported at F0 Index 86h/F6h[0].

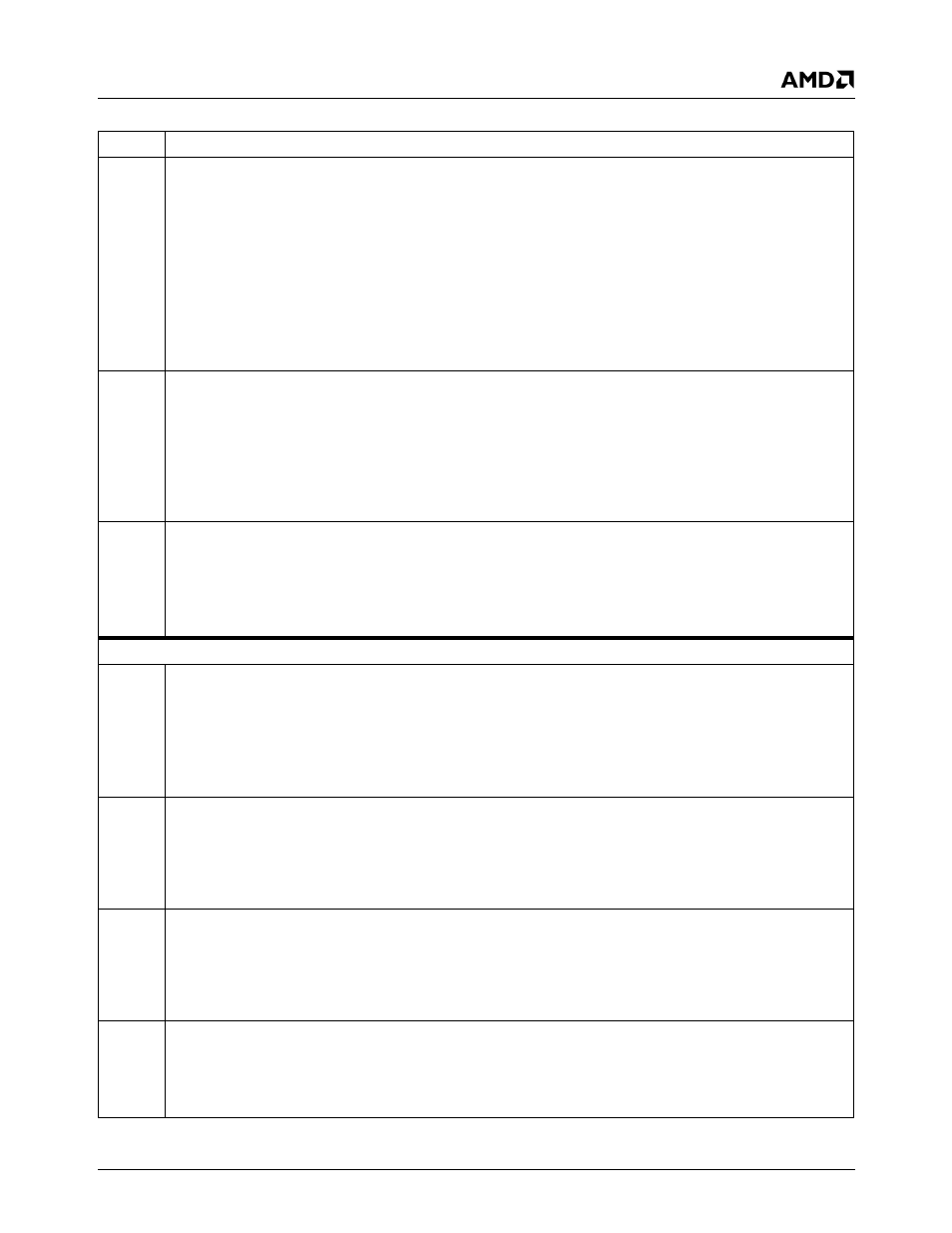

Index 83h

Power Management Enable Register 4 (R/W)

Reset Value: 00h

7

Secondary Hard Disk Idle Timer Enable. Turn on Secondary Hard Disk Idle Timer Count Register (F0 Index ACh) and

generate an SMI when the timer expires.

0: Disable.

1: Enable.

If an access occurs in the address ranges selected in F0 Index 93h[4], the timer is reloaded with the programmed count.

Top level SMI status is reported at F1BAR0+I/O Offset 00h/02h[0].

Second level SMI status is reported at F0 Index 86h/F6h[4].

6

Secondary Hard Disk Access Trap. If this bit is enabled and an access occurs in the address ranges selected in F0 Index

93h[4], an SMI is generated.

0: Disable.

1: Enable.

Top level SMI status is reported at F1BAR0+I/O Offset 00h/02h[0].

Second level SMI status is reported at F0 Index 86h/F6h[5].

5

ACPI Timer SMI. Allow SMI generation for MSB toggles on the ACPI Timer (F1BAR0+I/O Offset 1Ch or

F1BAR1+I/O Offset 1Ch).

0: Disable.

1: Enable.

Top level SMI status is reported at F1BAR0+I/O Offset 00h/02h[0].

Second level SMI status is reported at F0 Index 87h/F7h[0].

4

THRM# SMI. Allow SMI generation on assertion of THRM#.

0: Disable.

1: Enable.

Top level SMI status is reported at F1BAR0+I/O Offset 00h/02h[0].

Second level SMI status is reported at F0 Index 87h/F7h[6].

Table 6-29. F0: PCI Header/Bridge Configuration Registers for GPIO and LPC Support (Continued)

Bit

Description