3 power planes control, 4 power management events, Table 6-6 – AMD Geode SC2200 User Manual

Page 160: Power planes control signals vs. sleep states, Table 6-7, Power planes vs. sleep/global states, Table 6-8, Power management events, Cording to table 6-8

168

AMD Geode™ SC2200 Processor Data Book

Core Logic Module

32580B

6.2.9.3

Power Planes Control

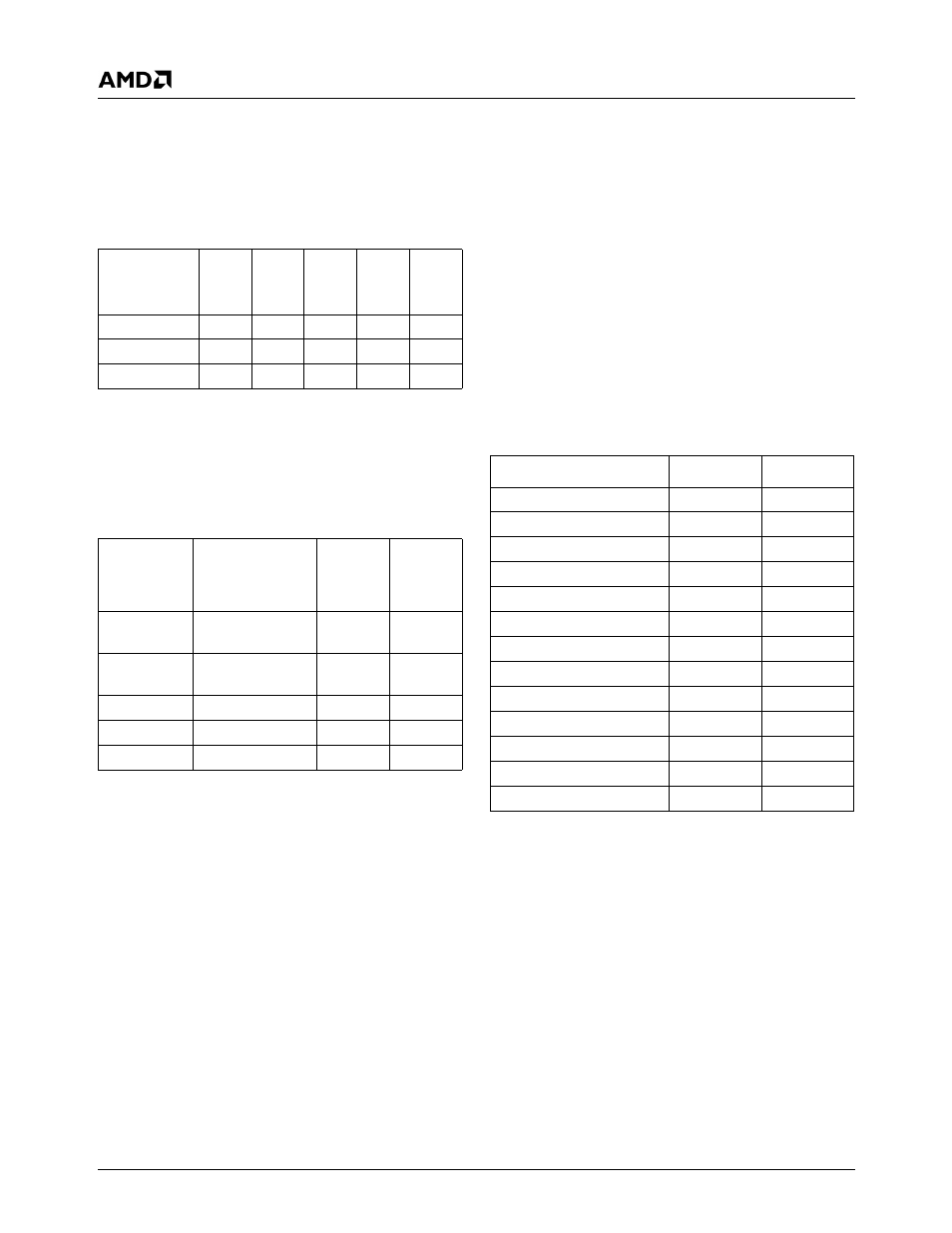

The SC2200 supports up to three power planes. Three sig-

nals are used to control these power planes. Table 6-6

describes the signals and when each is asserted.

These signals allow control of the power of system devices

and the SC2200 itself. Table 6-7 describes the SC2200

power planes with respect to the different Sleep and Global

states.

The SC2200 power planes are controlled externally by the

three signals (i.e., the system designer should make sure

the system design is such that Table 6-7 is met) for all sup-

ported Sleep states.

V

SB

and V

BAT

are not controlled by any control signal. V

SB

exists as long as the AC power is plugged in (for desktop

systems) or the main battery is charged (for mobile sys-

tems). V

BAT

exists as long as the RTC battery is charged.

The case in which V

SB

does not exist is called Mechanical

Off (G3).

6.2.9.4

Power Management Events

The SC2200 supports power management events that can

manage:

• Transition of the system from a Sleep state to a Work

state. This is done by the hardware. These events are

defined as wakeup events.

• Enabled wakeup events to set the WAK_STS bit

(F1BAR1+I/O Offset 08h[15]) to 1, when transitioning

the system back to the working state.

• Generation of an interrupt. This invokes the relevant

software driver. The interrupt can either be an SMI or

SCI (selected by the SCI_EN bit, F1BAR1+I/O Offset

0Ch[0]). These events are defined as interrupt events.

Table 6-8 lists the power management events that can gen-

erate an SCI or SMI.

Table 6-6. Power Planes Control Signals vs.

Sleep States

Signal

S0

SL1

SL2

SL3

SL4

and

SL5

PWRCNT1

1

1

0

0

0

PWRCNT2

1

1

1

0

0

ONCTL#

0

0

0

0

1

Table 6-7. Power Planes vs. Sleep/Global States

Sleep/

Global State

V

CORE

, V

CCCRT

,

V

I/O,

V

PLL

,

AV

CCCRT

V

SB

,

V

SBL

V

BAT

S0, SL1 and

SL2

On

On

On or Off

SL3, SL4

and SL5

Off

On

On or Off

G3

Off

Off

On

No Power

Off

Off

Off

Illegal

On

Off

On or Off

Table 6-8. Power Management Events

Event

SCI

SMI

Power Button

Yes

Yes

Power Button Override

Yes

-

Bus Master Request

Yes

-

Thermal Monitoring

Yes

Yes

USB

Yes

Yes

RTC

Yes

Yes

ACPI Timer

Yes

Yes

GPIO

Yes

Yes

SDATA_IN2 (AC97)

Yes

Yes

IRRX1

Yes

Yes

RI2#

Yes

Yes

GPWIO

Yes

Yes

Internal SMI signal

Yes

-