Intel PXA255 User Manual

Page 62

2-32

Intel® PXA255 Processor Developer’s Manual

System Architecture

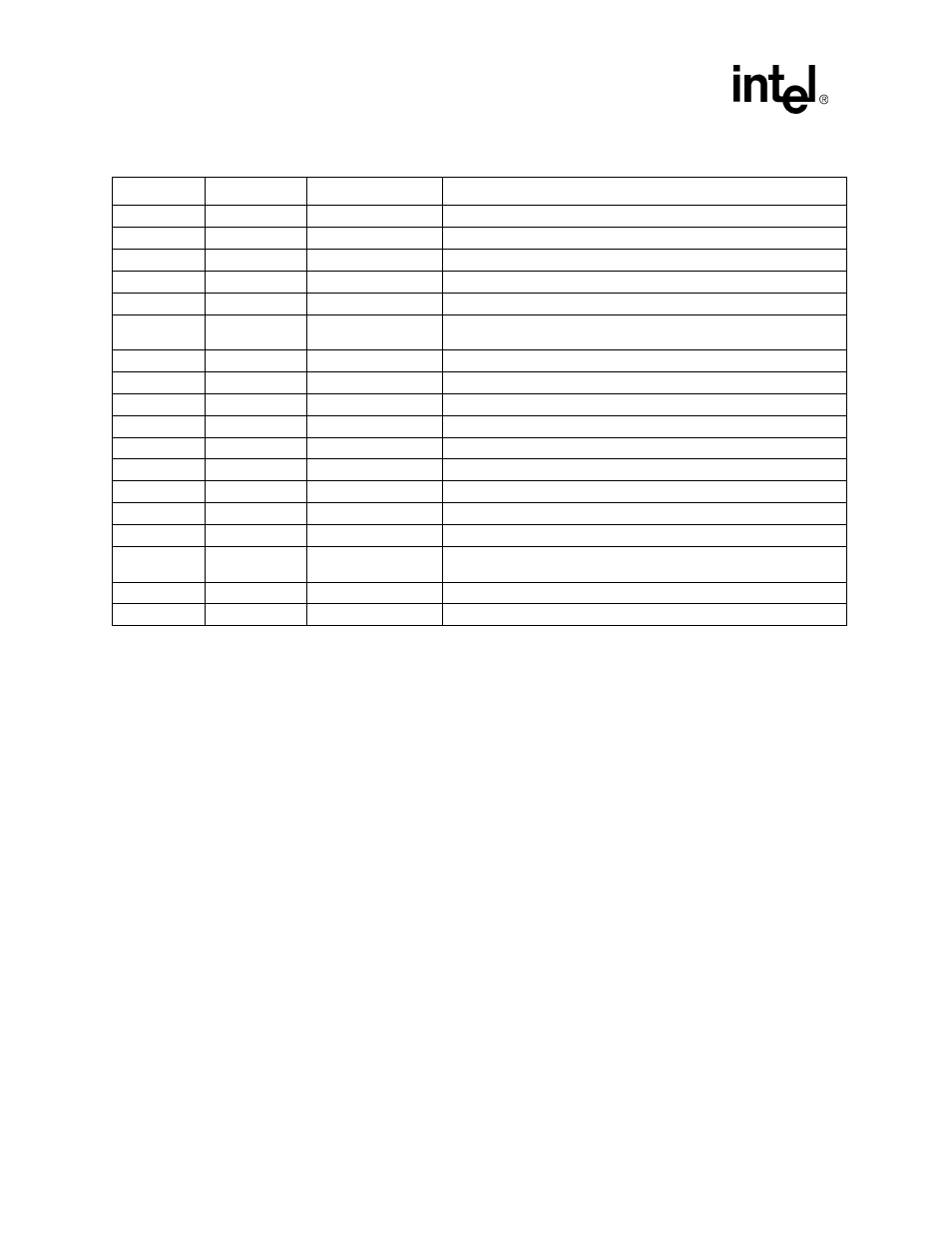

0x4800_0000

MDCNFG

SDRAM Configuration Register 0

0x4800_0004

MDREFR

SDRAM Refresh Control Register

0x4800_0008

MSC0

Static Memory Control Register 0

0x4800_000C

MSC1

Static Memory Control Register 1

0x4800_0010

MSC2

Static Memory Control Register 2

0x4800_0014

MECR

Expansion Memory (PCMCIA/Compact Flash) Bus Configuration

Register

0x4800_001C

SXCNFG

Synchronous Static Memory Control Register

0x4800_0024

SXMRS

MRS value to be written to SMROM

0x4800_0028

MCMEM0

Card interface Common Memory Space Socket 0 Timing Configuration

0x4800_002C

MCMEM1

Card interface Common Memory Space Socket 1 Timing Configuration

0x4800_0030

MCATT0

Card interface Attribute Space Socket 0 Timing Configuration

0x4800_0034

MCATT1

Card interface Attribute Space Socket 1 Timing Configuration

0x4800_0038

MCIO0

Card interface I/O Space Socket 0 Timing Configuration

0x4800_003C

MCIO1

Card interface I/O Space Socket 1 Timing Configuration

0x4800_0040

MDMRS

MRS value to be written to SDRAM

0x4800_0044

BOOT_DEF

Read-only Boot-Time Register. Contains BOOT_SEL and PKG SEL

values.

0x4800_0058

MDMRSLP

Low Power SDRAM Mode Register Set Configuration Register

0x4800_0064

SA1111CR

SA1111 Compatibility Register

Table 2-8. System Architecture Register Address Summary (Sheet 12 of 12)

Unit

Address

Register Symbol

Register Description