1 global control register (gcr), Gcr bit definitions -20, Table 13-7 – Intel PXA255 User Manual

Page 472

13-20

Intel® PXA255 Processor Developer’s Manual

AC’97 Controller Unit

Channel specific data registers are for FIFO accesses and the PCM, Modem, and Mic-in FIFOs

each have a register. A write access to one of these registers updates the written data in the

corresponding Transmit FIFO. A read access to one of these registers flushes out an entry from the

corresponding Receive FIFO.

Note: Register tables show organization and individual bit definitions. All reserved bits are read as

unknown values and must be written with a 0. A question mark indicates the value is unknown at

reset.

Note: Some register bits receive status from CODECs. The CODEC status sets the bit and software clears

the bit (write a one to clear). The status can come in at any time, even when the bit is set or during

a software clear. If software clears the bit as the CODEC status updates the bit, the CODEC status

event takes higher priority. The term “interruptible” denotes bits that can be affected by this

condition.

13.8.3.1

Global Control Register (GCR)

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

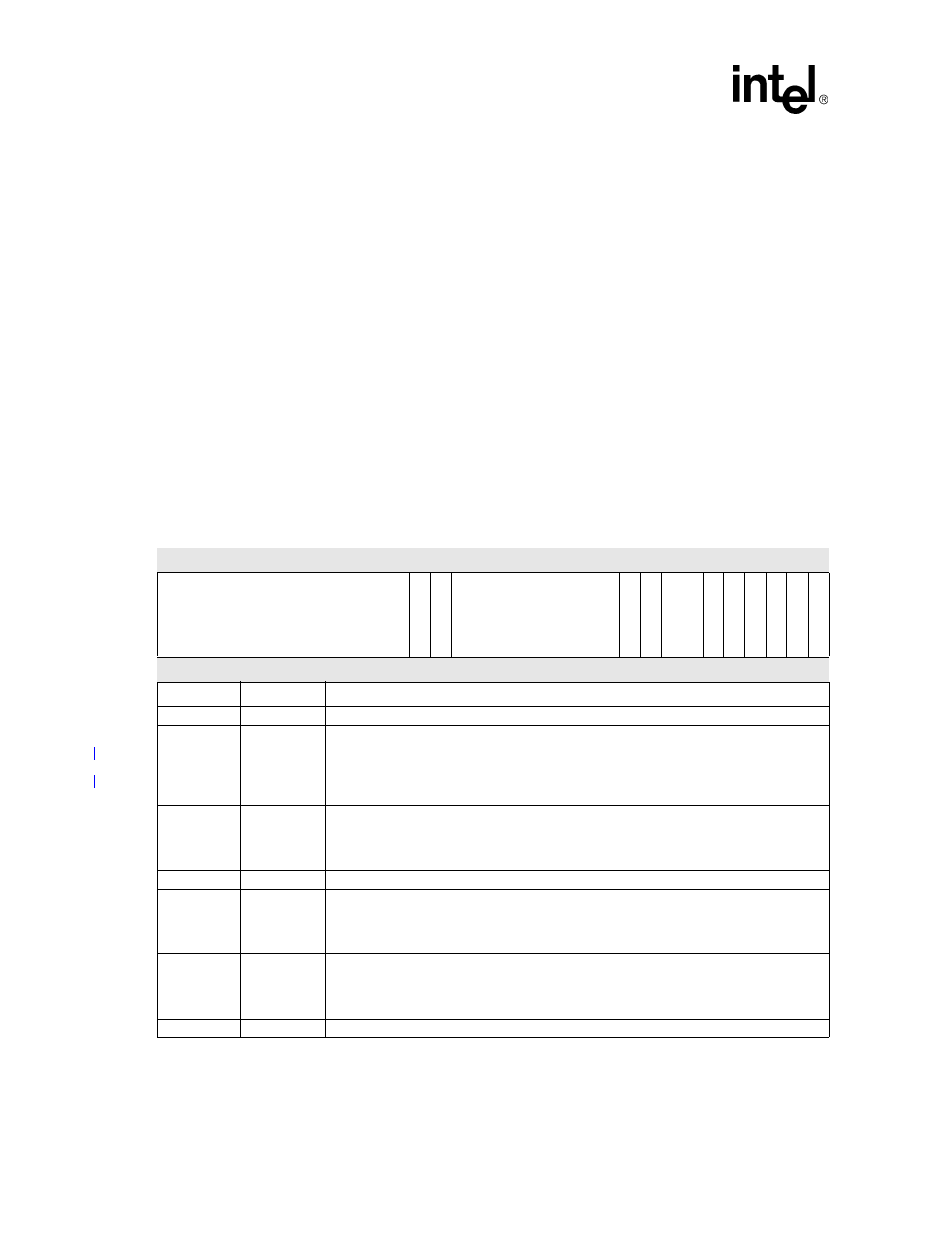

Table 13-7. GCR Bit Definitions (Sheet 1 of 2)

Physical Address

4050_000C

GCR Register

AC’97 Controller Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

CD

ON

E_

IE

SD

O

N

E_

IE

reserved

S

E

C

RDY

_

IEN

PR

IRD

Y

_

IEN

re

se

rv

e

d

SEC

RES

_

IEN

PR

IR

ES

_

IE

N

AC

L

INK

_O

F

F

WA

R

M

_

R

S

T

CO

L

D

_

R

ST

GI

E

Reset 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

31:20

—

reserved

19

CDONE_IE

Command Done Interrupt Enable (CDONE_IE):

0 = The ACUNIT does not trigger an interrupt to the CPU after sending the command

address and data to the CODEC.

1 = The ACUNIT triggers an interrupt to the CPU after sending the command address and

data to the CODEC.

18

SDONE_IE

Status Done Interrupt Enable (SDONE_IE):

0 = Interrupt is disabled

1 = Enables an interrupt to occur after receiving the status address and data from the

CODEC

17:10

—

reserved

9

SECRDY_IEN

Secondary Ready Interrupt Enable (SECRDY_IEN):

0 = Interrupt is disabled

1 = Enables an interrupt to occur when the Secondary CODEC sends the CODEC READY

bit on the SDATA_IN_1 pin

8

PRIRDY_IEN

Primary Ready Interrupt Enable (PRIRDY_IEN):

0 = Interrupt is disabled

1 = Enables an interrupt to occur when the Primary CODEC sends the CODEC READY bit

on the SDATA_IN_0 pin.

7:6

—

reserved