1 reset, 2 fifo operation, 1 reset -4 17.4.2 fifo operation -4 – Intel PXA255 User Manual

Page 576: Example nrz bit encoding – (0b0100 1011 -4

17-4

Intel® PXA255 Processor Developer’s Manual

Hardware UART

Receive data sample counter frequency is 16 times the value of the bit frequency. The 16X clock is

created by the baud rate generator. Each bit is sampled three times in the middle. Shaded bits in

are optional and can be programmed by software.

Each data frame is between seven and 12 bits long, depending on the size of the data programmed,

whether parity is enabled, and the number of stop bits. A data frame begins by transmitting a start

bit that is represented by a high to low transition. The start bit is followed by data that is five to

eight bits wide and begins with the least significant bit (LSB). The data bits are followed by an

optional parity bit. The parity bit is set if even parity is enabled and the data byte has an odd

number of ones or if odd parity is enabled and the data byte has an even number of ones. The data

frame ends with one, one and a half, or two stop bits, as programmed by software. The stop bits are

represented by one, one and a half, or two successive bit periods of a logic one.

The UART has two FIFOs: one transmit and one receive. The transmit FIFO is 64 bytes deep and

eight bits wide. The receive FIFO is 64 bytes deep and 11 bits wide. Three bits are used for tracking

errors.

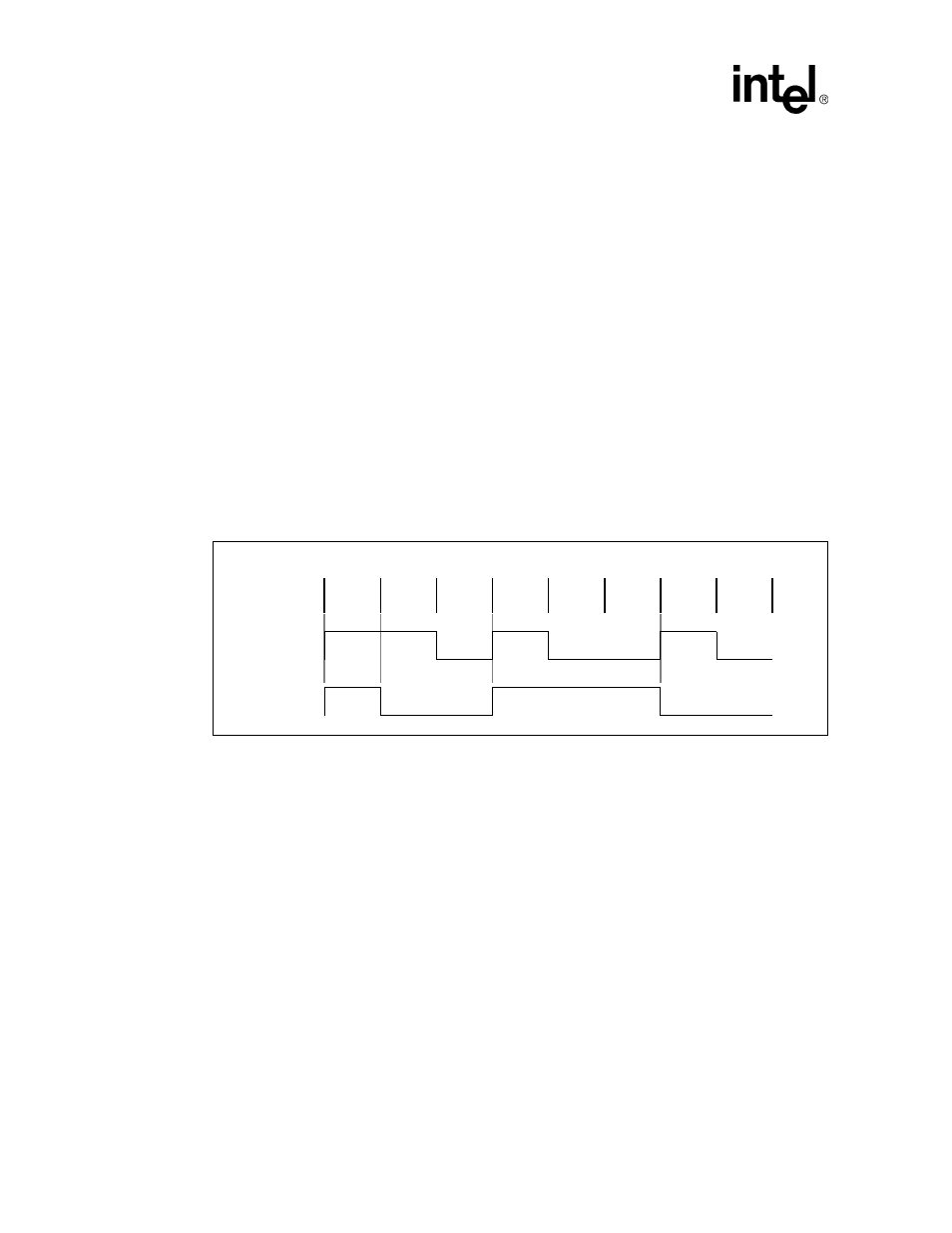

The UART can use NRZ coding to represent individual bit values. NRZ coding is enabled when

Interrupt Enable register (IER) bit 5 (IER[5]) is set to high. A one is represented by a line transition

and a zero is represented by no line transition.

shows the data byte 0b 0100 1011 in

NRZ coding. The LSB is transmitted first.

17.4.1

Reset

The UART is disabled on reset. To enable the UART, use software to program the GPIO registers

then set IER[UUE]. When the UART is enabled, the receiver waits for a frame start bit and the

transmitter sends data if it is available in the Transmit Holding register. Transmit data can be

written to the Transmit Holding register before the UART is enabled. In FIFO mode, data is

transmitted from the FIFO to the Transmit Holding register before it goes to the pin.

When the UART unit is disabled, the transmitter or receiver finishes the current byte and stops

transmitting or receiving data. When the UART is enabled, data in the FIFO is not cleared and

transmission resumes.

17.4.2

FIFO Operation

The UART has a transmit FIFO and a receive FIFO each holding 64 characters of data. There are

three separate methods for moving data into and out of the FIFOs: interrupts, polling, and DMA.

Figure 17-2. Example NRZ Bit Encoding – (0b0100 1011

Digital

Data

NRZ

Data

Bit

Value

1

1

0

1

0

0

1

0

LSB

MSB