8 lcd controller interrupt id register (liidr), Lcd controller interrupt id register (liidr) -41, Liicr bit definitions -41 – Intel PXA255 User Manual

Page 305

Intel® PXA255 Processor Developer’s Manual

7-41

LCD Controller

7.6.8

LCD Controller Interrupt ID Register (LIIDR)

, contains a copy of the Frame ID Register (FIDR) from the descriptor

currently being processed when a start of frame (SOF), end of frame (EOF), branch (BS), or bus

error (BER) interrupt is signalled. LIIDR is written to only when an unmasked interrupt of the

above type is signalled and there are no other unmasked interrupts in the LCD controller pending.

As such, the register is considered to be sticky and will be overwritten only when the signalled

interrupt is cleared by writing the LCD controller status register. Except for a bus error, in dual

panel mode LIIDR is written only when both channels have reached a given state. LIIDR is written

with the last channel to reach that state. (i.e. FIDR of the last channel to reach SOF would be

written in LIIDR if SOF interrupts are enabled).

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

2

BER

Bus error status, nonmaskable interrupt:

0 = DMA has not attempted an access to reserved/nonexistent memory space.

1 = DMA has attempted an access to a reserved/nonexistent location in external memory.

1

SOF

Start Of Frame status, maskable interrupt:

0 = A new frame descriptor with its SOFINT bit set has not been fetched.

1 = The DMA has begun fetching a new frame with its SOFINT bit set.

0

LDD

LCD Disable Done status, maskable interrupt:

0 = LCD has not been disabled or the last active frame completed.

1 = LCD has been disabled and the last active frame has completed.

Table 7-12. LCSR Bit Definitions (Sheet 2 of 2)

Physical Address

0x4400_0038

LCD Controller Status Register 1

LCD Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

SI

N

T

BS

EO

F

QD

OU

IU

U

IU

L

AB

C

BER

SO

F

LD

D

Reset X X X X X X X X X X X X X X X X X X X X X 0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

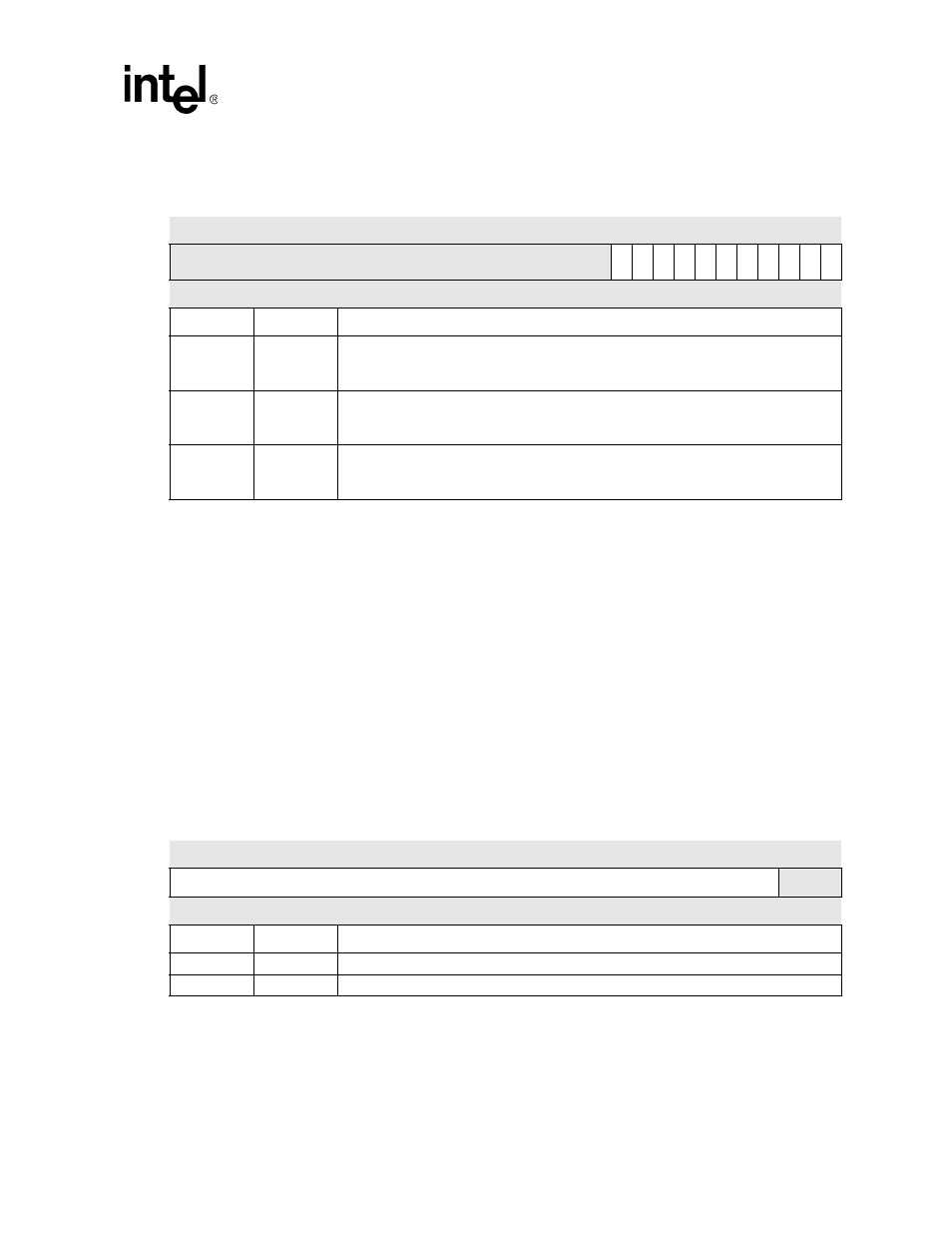

Table 7-13. LIICR Bit Definitions

Physical Address

0x4400_003C

LCD Controller Interrupt ID

Register

LCD Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

IFRAMEID

reserved

Reset ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? X X X

Bits

Name

Description

31:3

IFRAMEID

Interrupt Frame ID

2:0

—

reserved