Ier bit definitions -12, Table 17-6 – Intel PXA255 User Manual

Page 584

17-12

Intel® PXA255 Processor Developer’s Manual

Hardware UART

Enabling DMA requests also enables a separate error interrupt. For additional information see

Set bit 7 of the IER to enable DMA requests. The IER also contains the unit enable and NRZ

coding enable control bits. Bits 7 through 4 are used differently from the standard 16550A register

definition.

Note: MCR[OUT2] is a global interrupt enable, and must be set to enable UART interrupts.

Note: To ensure that the DMA controller and programmed I/O do not access the same FIFO, software

must not set DMAE (bit 7) while TIE (bit 1) or RAVIE (bit 0) are set to 1.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

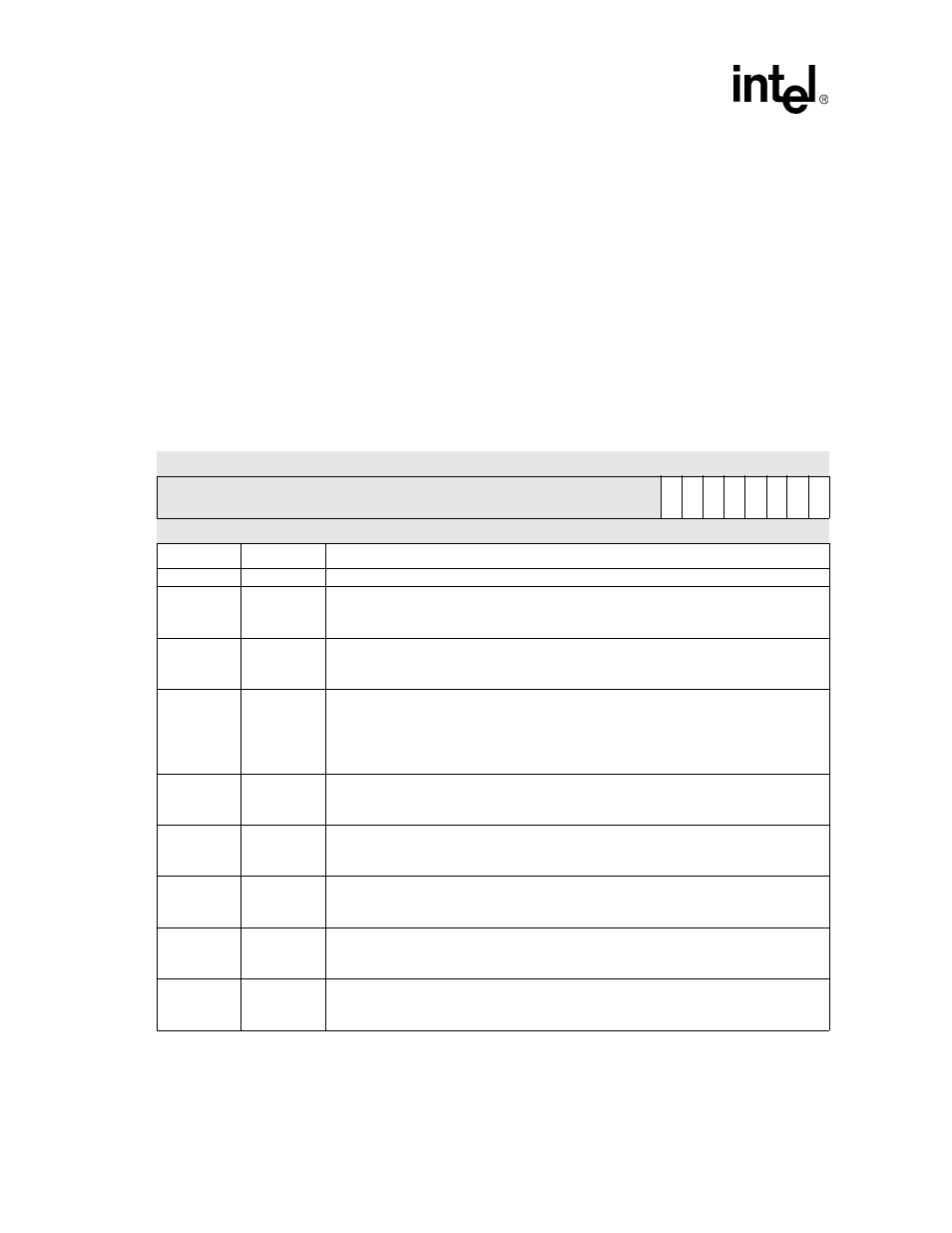

Table 17-6. IER Bit Definitions

Physical Address

0x4160_0004

Interrupt Enable Register (IER)

PXA255 Processor Hardware UART

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

DM

AE

UU

E

NR

Z

E

RT

OI

E

MI

E

RL

S

E

TIE

RA

VI

E

Reset ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?

0

0

0

0

0

0

0

0

Bits

Name

Description

31:8

—

reserved

7

DMAE

DMA REQUESTS ENABLE:

0 = DMA requests are disabled

1 = DMA requests are enabled

6

UUE

UART Unit Enable:

0 = the unit is disabled

1 = the unit is enabled

5

NRZE

NRZ CODING ENABLE.

NRZ encoding/decoding is only used in UART mode, not in infrared mode. If the slow

infrared receiver or transmitter is enabled, NRZ coding is disabled.

0 = NRZ coding disabled

1 = NRZ coding enabled

4

RTOIE

RECEIVER TIME OUT INTERRUPT ENABLE (Source IIR[TOD]):

0 = Receiver data Time out Interrupt disabled

1 = Receiver data Time out Interrupt enabled

3

MIE

MODEM INTERRUPT ENABLE (Source IIR[IID]):

0 = Modem Status Interrupt disabled

1 = Modem Status Interrupt enabled

2

RLSE

RECEIVER LINE STATUS INTERRUPT ENABLE (Source IIR[IID]):

0 = Receiver Line Status Interrupt disabled

1 = Receiver Line Status Interrupt enabled

1

TIE

TRANSMIT DATA REQUEST INTERRUPT ENABLE (Source IIR[IID]):

0 = Transmit FIFO Data Request Interrupt disabled

1 = Transmit FIFO Data Request Interrupt enabled

0

RAVIE

RECEIVER DATA AVAILABLE INTERRUPT ENABLE (Source IIR[IID]):

0 = Receiver Data Available (trigger threshold reached) Interrupt disabled

1 = Receiver Data Available (trigger threshold reached) Interrupt enabled