5 ficp status register 0 (icsr0), 5 ficp status register 0 (icsr0) -13, Icsr0 bit definitions -13 – Intel PXA255 User Manual

Page 399

Intel® PXA255 Processor Developer’s Manual

11-13

Fast Infrared Communication Port

11.3.5

FICP Status Register 0 (ICSR0)

The ICSR0, shown in

, contains bits that signal the transmit FIFO service request,

receive FIFO service request, receiver abort, transmit FIFO underrun, framing error, and the end/

error in receive FIFO conditions. Each of these hardware-detected events signal an interrupt

request to the interrupt controller.

If a bit signals an interrupt request, it signals the interrupt request as long as the bit is set. When the

bit is cleared, the interrupt is cleared. Read/write bits are called status bits. Read-only bits are

called flags. Status bits that must be cleared by software after they are set by hardware are called

sticky status bits. Writing a 1 to a sticky status bit clears it. Writing a 0 to a sticky status bit has no

effect. Read-only flags are set and cleared by hardware. Writes to read-only flags have no effect.

Some bits that cause interrupts have corresponding mask bits in the control registers.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

.

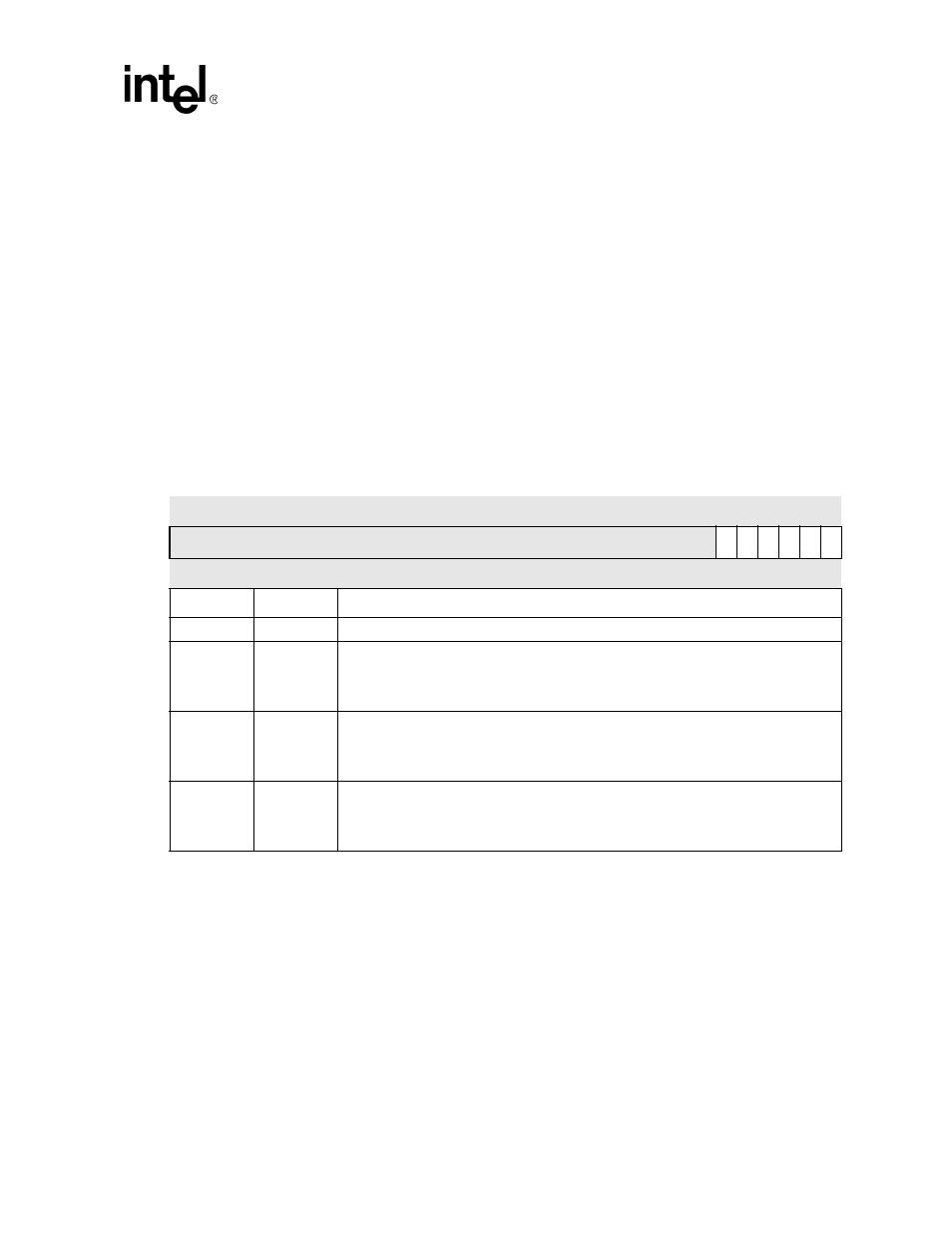

Table 11-6. ICSR0 Bit Definitions (Sheet 1 of 2)

0x4080_0014

Fast Infrared Communication Port

Status Register 0 (ICSR0)

Fast Infrared Communication Port

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

FR

E

RF

S

TF

S

RA

B

TU

R

EIF

Reset 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

[31:6]

—

reserved

5

FRE

Framing error.

0 = No framing errors encountered in the receipt of this data.

1 = Framing error occurred. A preamble was followed by something other than another

preamble or start flag, request interrupt.

4

RFS

Receive FIFO service request (read-only).

0 = Receive FIFO has not reached it trigger level or receiver disabled.

1 = Receive FIFO has reached its trigger level and receiver is enabled. DMA service

request signalled. Interrupt request signalled if not masked by ICCR0[RIE].

3

TFS

Transmit FIFO service request (read-only).

0 = Transmit FIFO has more than 96 entries of data or transmitter disabled.

1 = Transmit FIFO has 96 or less entries of data and transmitter is enabled. DMA service

request signalled. Interrupt request signalled if not masked by ICCR0[TIE].