Sa-1111 register bit definitions -45, Based on dqm[3:0, Dqm[1:0 – Intel PXA255 User Manual

Page 227

Intel® PXA255 Processor Developer’s Manual

6-45

Memory Controller

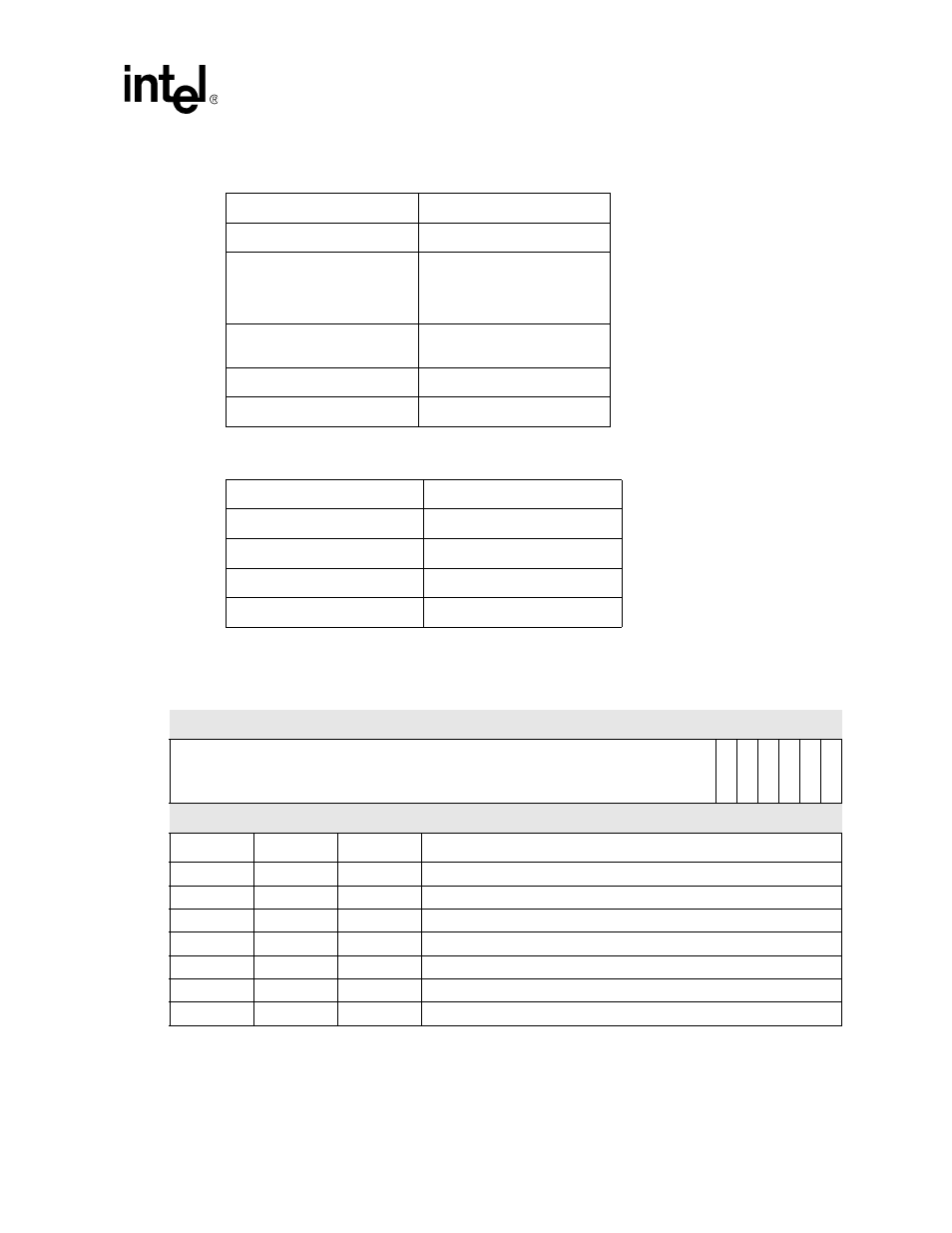

Table 6-21. 32-Bit Byte Address Bits MA[1:0] for Reads Based on DQM[3:0]

DQM[3:0]

MA[1:0]

0000

00

0001

1101

1001

0101

01

1011

0011

10

0111

11

Anything Else

00

Table 6-22. 16-Bit Byte Address Bit MA[0] for Reads Based on DQM[1:0]

DQM[1:0]

MA[0]

00

0

10

0

01

1

11

0

Table 6-23. SA-1111 Register Bit Definitions

0X4800 0064

SA1111

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

Re

se

rv

e

d

S

A

11

11

_

5

S

A

11

11

_

4

S

A

11

11

_

3

S

A

11

11

_

2

S

A

11

11

_

1

S

A

11

11

_

0

Reset ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?

0

0

0

0

0

0

Bits

Access

Name

Description

31:6

—

Reserved

Writes must set this field to zero and Read values should be ignored

5

R/W

SA1111_5

Enables SA-1111 Compatibility Mode for Static Memory Partition 5.

4

R/W

SA1111_4

Enables SA-1111 Compatibility Mode for Static Memory Partition 4.

3

R/W

SA1111_3

Enables SA-1111 Compatibility Mode for Static Memory Partition 3.

2

R/W

SA1111_2

Enables SA-1111 Compatibility Mode for Static Memory Partition 2.

1

R/W

SA1111_1

Enables SA-1111 Compatibility Mode for Static Memory Partition 1.

0

R/W

SA1111_0

Enables SA-1111 Compatibility Mode for Static Memory Partition 0.