13 modem status register (msr), 13 modem status register (msr) -23, 17 msr bit definitions -23 – Intel PXA255 User Manual

Page 595: Table 17-17

Intel® PXA255 Processor Developer’s Manual

17-23

Hardware UART

17.5.13

Modem Status Register (MSR)

The MSR, shown in

, provides the current state of the control lines from the modem or

data set (or a peripheral device emulating a modem) to the processor. In addition to this current

state information, four bits of the MSR provide change information. MSR[3:0] are set when a

control input from the modem changes state. They are cleared when the processor reads the MSR.

The status of the modem control lines do not affect the FIFOs. To use these lines for flow control,

IER[MIE] must be set. When an interrupt on one of the flow control pins occurs, the interrupt

service routine must disable the UART. The UART continues transmission and reception of the

current character and then stops. The contents of the FIFOs is preserved. If the UART is re-

enabled, transmission continues where it stopped.

Note: When bit 0, 1, 2, or 3 is set, a modem status interrupt is generated if IER[MIE] is set.

This is a read-only register. Ignore reads from reserved bits.

1

RTS

REQUEST TO SEND

Controls the status of the nRTS pin when the AFE bit is clear. When AFE is set, switches

between full autoflow and half autoflow.

Autoflow mode disabled:

0 = nRTS pin is 1

1 = nRTS pin is 0

Autoflow mode enabled:

0 = Auto-RTS disabled. Auto flow works only with auto-CTS

1 = Auto-RTS enabled. Auto flow works with both auto-CTS and auto-RTS

In loopback mode, controls status of CTS input signal.

0

—

reserved

Table 17-16. MCR Bit Definitions (Sheet 2 of 2)

Physical Address

0x4160_0010

Modem Control Register (MCR)

PXA255 Processor Hardware UART

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

AF

E

L

OOP

OUT

2

re

ser

ved

RT

S

re

ser

ved

Reset ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?

0

0

0 ?

0 ?

Bits

Name

Description

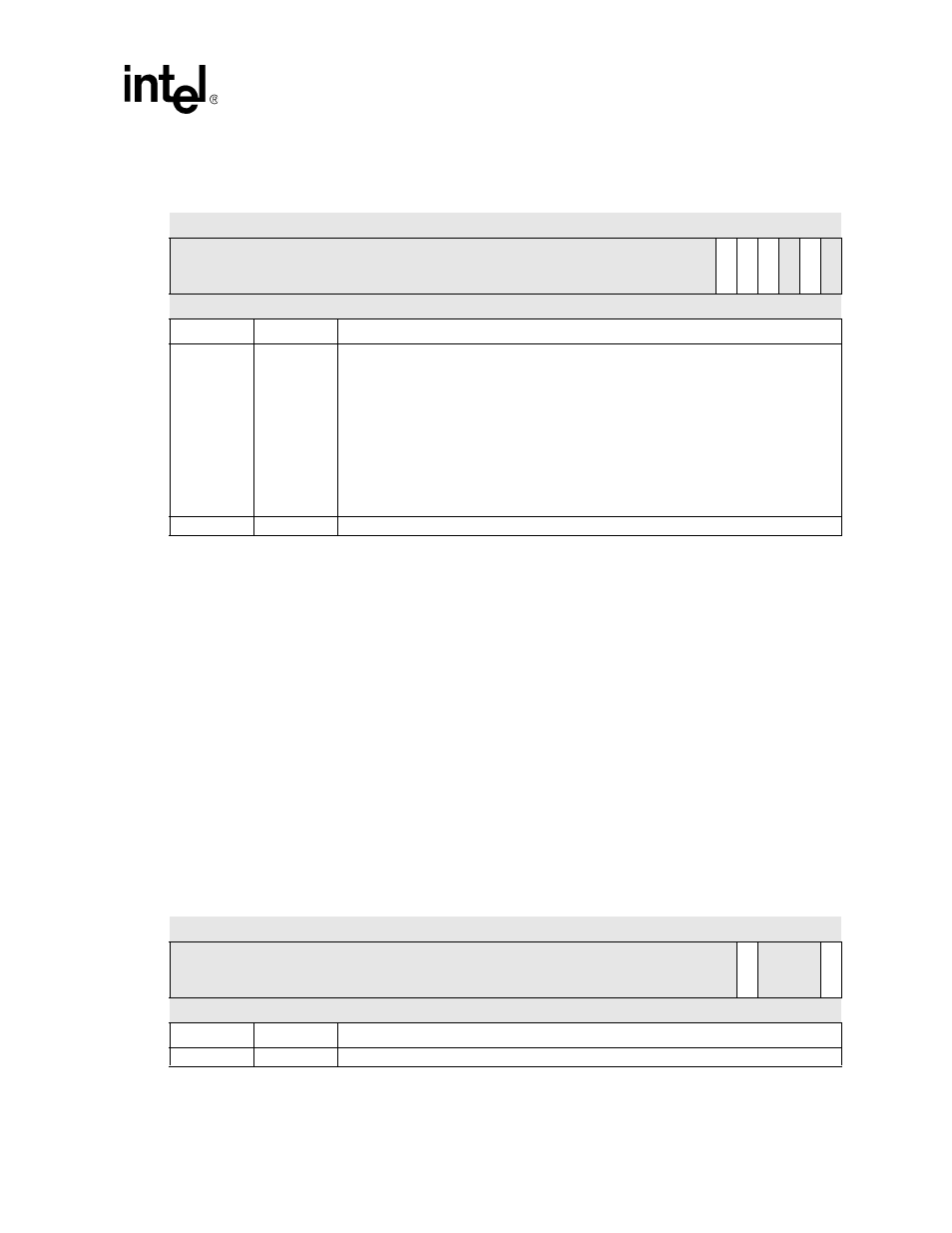

Table 17-17. MSR Bit Definitions (Sheet 1 of 2)

Physical Address

0x4160_0018

Modem Status Register (MSR)

PXA255 Processor Hardware UART

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

CT

S

reser

ved

DCT

S

Reset ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 1

? ? ?

0

Bits

Name

Description

31:5

—

reserved