2 external frame buffer, External frame buffer -11, Palette buffer format -11 – Intel PXA255 User Manual

Page 275: 1 bit per pixel data memory organization -11, Figure 7-5

Intel® PXA255 Processor Developer’s Manual

7-11

LCD Controller

7.4.2

External Frame Buffer

The external frame buffer is an off-chip memory area used to supply enough encoded pixel values to fill

the entire screen one or more times. The number of pixel data values depends on the size of the

screen (for example, 640 x 480 = 307,200 encoded pixel values).

show the memory organization within the frame buffer for each size pixel encoding.

In the following figures, “Base” refers to the initial address programmed in the FSADR register,

“Palette Buffer Index” refers to the data that specifies the location in the palette buffer, and “Raw

Pixel Data” refers to the actual 16-bit RGB data when the palette RAM is bypassed.

Figure 7-6. 1 Bit Per Pixel Data Memory Organization

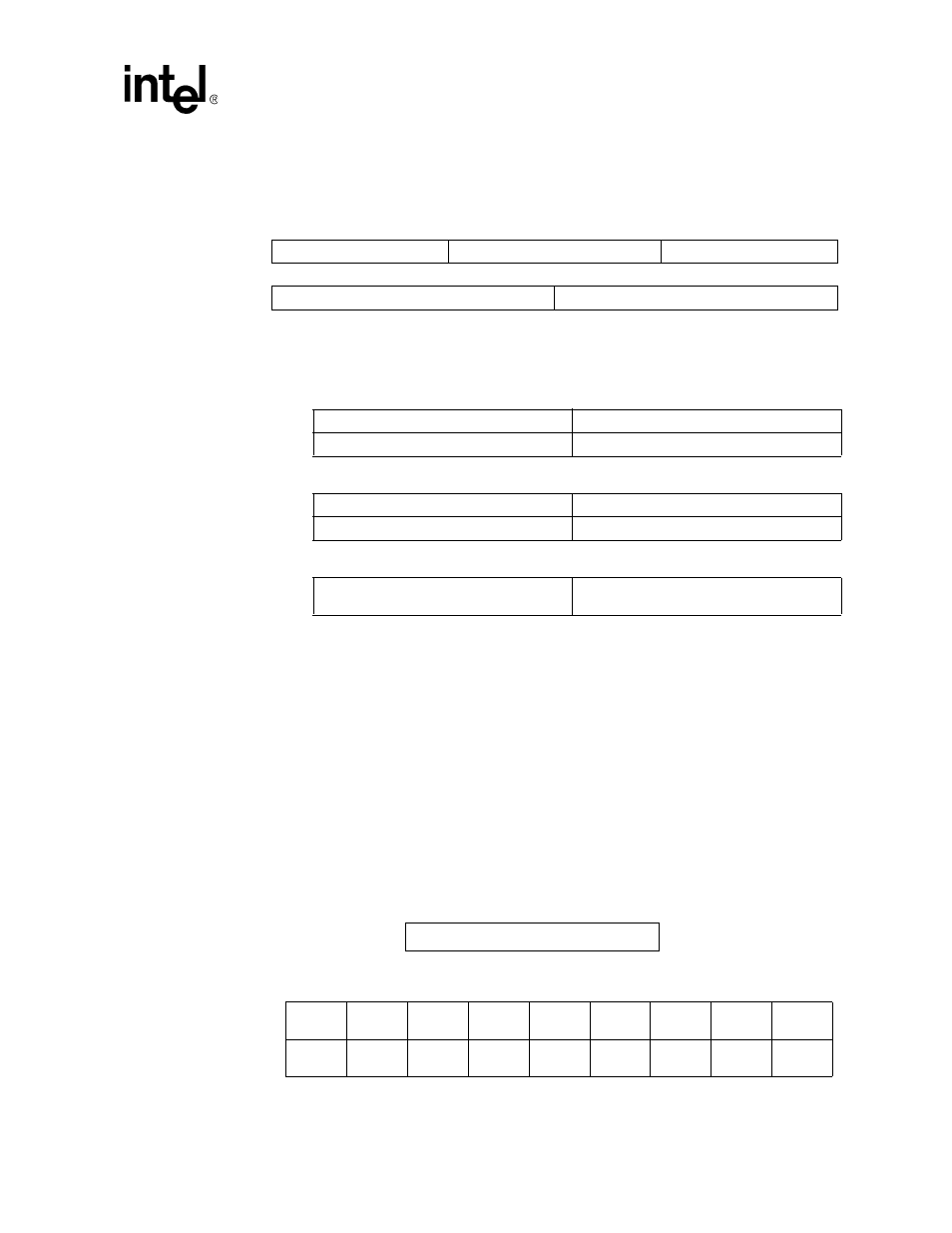

Figure 7-5. Palette Buffer Format

Individual Palette Entry

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Color

Red (R)

Green (G)

Blue (B)

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Mono

unused

Monochrome (M)

Little Endian Palette Entry Ordering

4-, 16- or 256-Entry Palette Buffer

Bit

31

16

15

0

Base + 0x0

Palette entry 1

Palette entry 0

Base + 0x4

Palette entry 3

Palette entry 2

Entries 4 through 255 do not exist for 1 and 2

bits/pixel.

Base + 0x1C

Palette entry 15

Palette entry 14

Base + 0x20

Palette entry 17

Palette entry 16

Entries 16 through 255 do not exist for

1, 2, and 4 bits/pixel.

Base +

0x1FC

Palette entry 255

Palette entry 254

Bit

0

1 bit/pixel

Palette Buffer Index[0]

Bit

31

30

29

28

...

3

2

1

0

Base +

0x0

Pixel 31

Pixel 30

Pixel 29

Pixel 28

...

Pixel 3

Pixel 2

Pixel 1

Pixel 0

Base +

0x4

Pixel 63

Pixel 62

Pixel 61

Pixel 60

...

Pixel 35

Pixel 34

Pixel 33

Pixel 32