5 interrupt controller pending register (icpr), Icpr bit definitions -25, Section 4.2.2.5 – Intel PXA255 User Manual

Page 129

Intel® PXA255 Processor Developer’s Manual

4-25

System Integration Unit

4.2.2.5

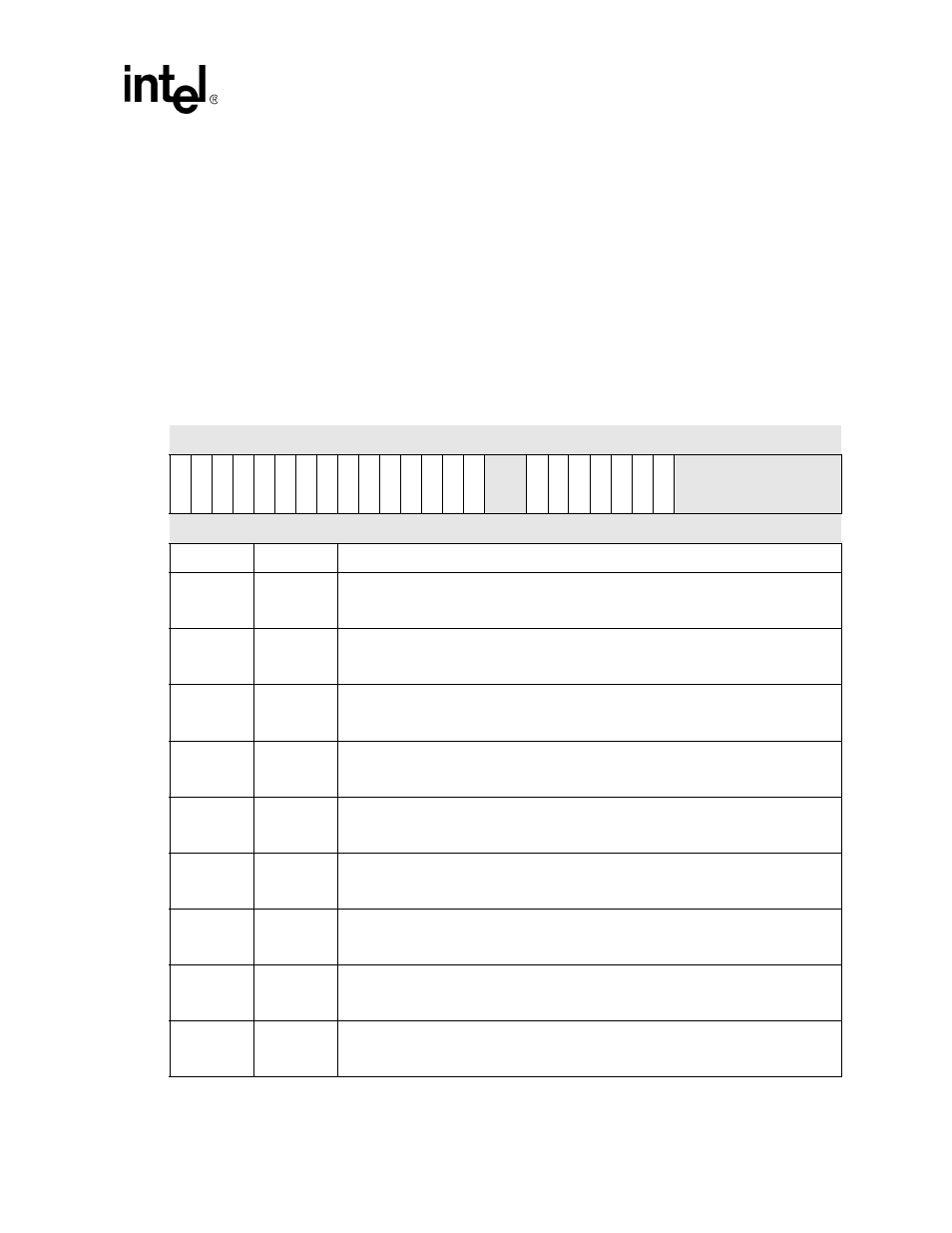

Interrupt Controller Pending Register (ICPR)

The ICPR, shown in

, is a 32-bit read-only register that shows all active interrupts in the

system. These bits are not affected by the state of the mask register (ICMR). Clearing the interrupt

status bit at the source, automatically clears the corresponding ICPR flag, provided there are no

other interrupt status bits set within the source unit.

shows the pending interrupt source assigned to each bit position in the ICPR. Also

included in the table are the source units for the interrupts and the number of second-level

interrupts associated with each. For more information on the second-level interrupts, see the

section that corresponds to its name in the Source Unit column.

Table 4-35. ICPR Bit Definitions (Sheet 1 of 3)

Physical Address

0x40D0_0010

ICPR

System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

IS31

IS30

IS29

IS28

IS27

IS26

IS25

IS24

IS23

IS22

IS21

IS20

IS19

IS18

IS17

reser

ved

IS14

IS13

IS12

IS1

1

IS10

IS9

IS8

reser

ved

Reset 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

<31>

IS31

RTC Alarm Match Register Interrupt Pending

0 – Interrupt NOT pending due to RTC Alarm Match Register.

1 – Interrupt pending due to RTC Alarm Match Register.

<30>

IS30

RTC HZ Clock Tick Interrupt Pending

0 – Interrupt NOT pending due to RTC HZ Clock Tick.

1 – Interrupt pending due to RTC HZ Clock Tick.

<29>

IS29

OS Timer Match Register 3 Interrupt Pending

0 – Interrupt NOT pending due to OS Timer Match Register 3.

1 – Interrupt pending due to OS Timer Match Register 3.

<28>

IS28

OS Timer Match Register 2 Interrupt Pending

0 – Interrupt NOT pending due to OS Timer Match Register 2.

1 – Interrupt pending due to OS Timer Match Register 2.

<27>

IS27

OS Timer Match Register 1 Interrupt Pending

0 – Interrupt NOT pending due to OS Timer Match Register 1.

1 – Interrupt pending due to OS Timer Match Register 1.

<26>

IS26

OS Timer Match Register 0 Interrupt Pending

0 – Interrupt NOT pending due to OS Timer Match Register 0.

1 – Interrupt pending due to OS Timer Match Register 0.

<25>

IS25

DMA Channel Service Request Interrupt Pending

0 – Interrupt NOT pending due to DMA Channel Service Request.

1 – Interrupt pending due to DMA Channel Service Request.

<24>

IS24

SSP Service Request Interrupt Pending

0 – Interrupt NOT pending due to SSP Service Request.

1 – Interrupt pending due to SSP Service Request.

<23>

IS23

MMC Status/Error Detection Interrupt Pending

0 – Interrupt NOT pending due to MMC Status/Error Detection.

1 – Interrupt pending due to MMC Status/Error Detection.