Intel PXA255 User Manual

Page 42

2-12

Intel® PXA255 Processor Developer’s Manual

System Architecture

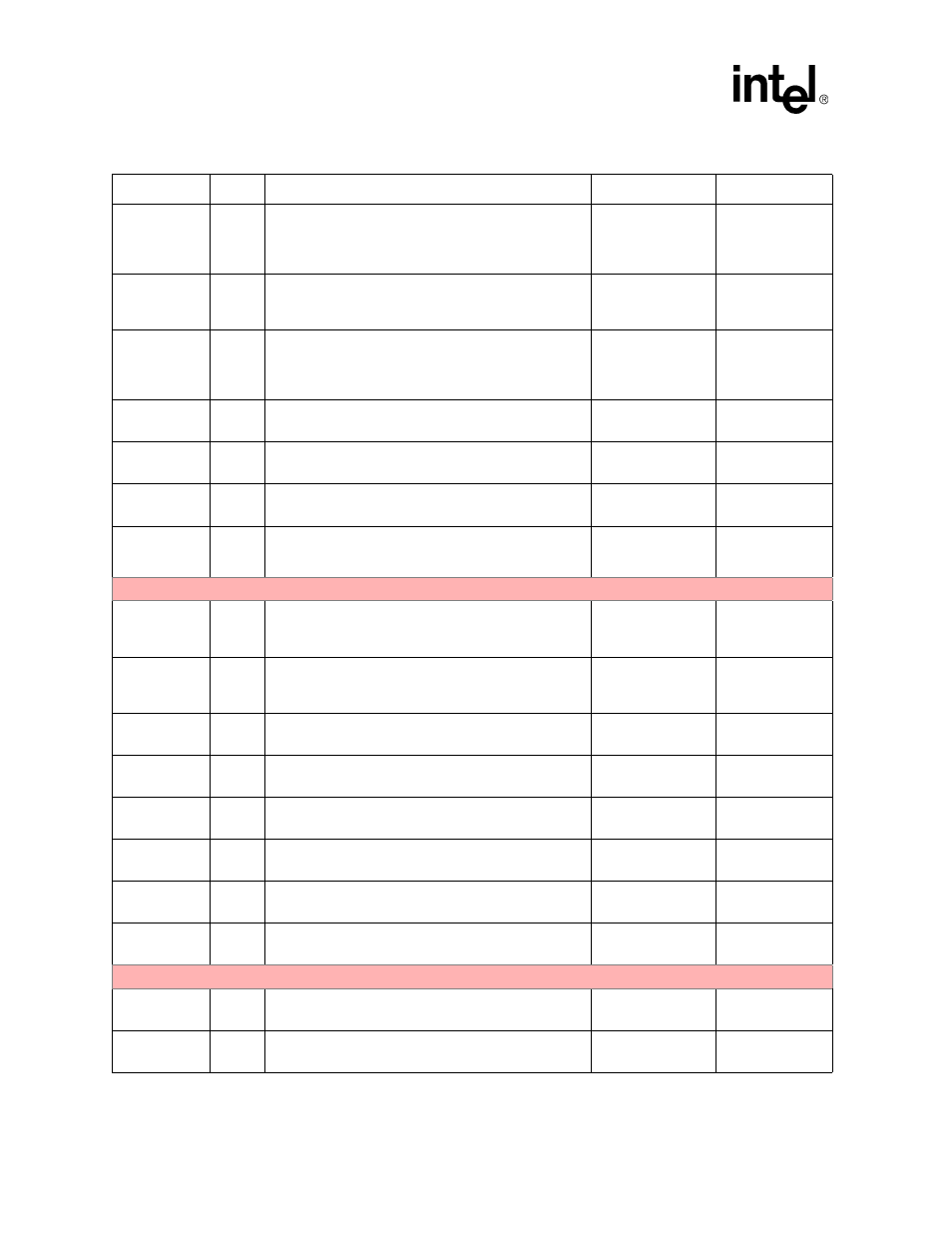

L_DD[13]/

GPIO[71]

ICOCZ

LCD display data. (output) Transfers pixel information

from the LCD Controller to the external LCD panel.

3.6864 MHz clock. (output) Output from 3.6864 MHz

oscillator.

Pulled High -

Note[1]

Note [3]

L_DD[14]/

GPIO[72]

ICOCZ

LCD display data. (output) Transfers pixel information

from the LCD Controller to the external LCD panel.

32 kHz clock. (output) Output from the 32 kHz oscillator.

Pulled High -

Note[1]

Note [3]

L_DD[15]/

GPIO[73]

ICOCZ

LCD display data. (output) Transfers pixel information

from the LCD Controller to the external LCD panel.

Memory Controller grant. (output) Notifies an external

device it has been granted the system bus.

Pulled High -

Note[1]

Note [3]

L FCLK/

GPIO[74]

ICOCZ

LCD frame clock. (output) Indicates the start of a new

frame. Also referred to as Vsync.

Pulled High -

Note[1]

Note [3]

L LCLK/

GPIO[75]

ICOCZ

LCD line clock. (output) Indicates the start of a new line.

Also referred to as Hsync.

Pulled High -

Note[1]

Note [3]

L PCLK/

GPIO[76]

ICOCZ

LCD pixel clock. (output) Clocks valid pixel data into the

LCD’s line shift buffer.

Pulled High -

Note[1]

Note [3]

L BIAS/

GPIO[77]

ICOCZ

AC bias drive. (output) Notifies the panel to change the

polarity for some passive LCD panel. For TFT panels,

this signal indicates valid pixel data.

Pulled High -

Note[1]

Note [3]

Full Function UART Pins

FFRXD/

GPIO[34]

ICOCZ

Full Function UART Receive. (input)

MMC chip select 0. (output) Chip select 0 for the MMC

Controller.

Pulled High -

Note[1]

Note [3]

FFTXD/

GPIO[39]

ICOCZ

Full Function UART Transmit. (output)

MMC chip select 1. (output) Chip select 1 for the MMC

Controller.

Pulled High -

Note[1]

Note [3]

FFCTS/

GPIO[35]

ICOCZ

Full Function UART Clear-to-Send. (input)

Pulled High -

Note[1]

Note [3]

FFDCD/

GPIO[36]

ICOCZ

Full Function UART Data-Carrier-Detect. (input)

Pulled High -

Note[1]

Note [3]

FFDSR/

GPIO[37]

ICOCZ

Full Function UART Data-Set-Ready. (input)

Pulled High -

Note[1]

Note [3]

FFRI/

GPIO[38]

ICOCZ

Full Function UART Ring Indicator. (input)

Pulled High -

Note[1]

Note [3]

FFDTR/

GPIO[40]

ICOCZ

Full Function UART Data-Terminal-Ready. (output)

Pulled High -

Note[1]

Note [3]

FFRTS/

GPIO[41]

ICOCZ

Full Function UART Request-to-Send. (output)

Pulled High -

Note[1]

Note [3]

Bluetooth UART Pins

BTRXD/

GPIO[42]

ICOCZ

Bluetooth UART Receive. (input)

Pulled High -

Note[1]

Note [3]

BTTXD/

GPIO[43]

ICOCZ

Bluetooth UART Transmit. (output)

Pulled High -

Note[1]

Note [3]

Table 2-6. Pin & Signal Descriptions for the PXA255 Processor (Sheet 4 of 9)

Pin Name

Type

Signal Descriptions

Reset State

Sleep State