Gpdr0 bit definitions -9, Gpdr1 bit definitions -9, Gpdr2 bit definitions -9 – Intel PXA255 User Manual

Page 113: Table 4-6, Table 4-7, Table 4-8

Intel® PXA255 Processor Developer’s Manual

4-9

System Integration Unit

4.1.3.3

GPIO Pin Output Set Registers (GPSR0, GPSR1, and GPSR2) and Pin

Output Clear Registers (GPCR0, GPCR1, GPCR2)

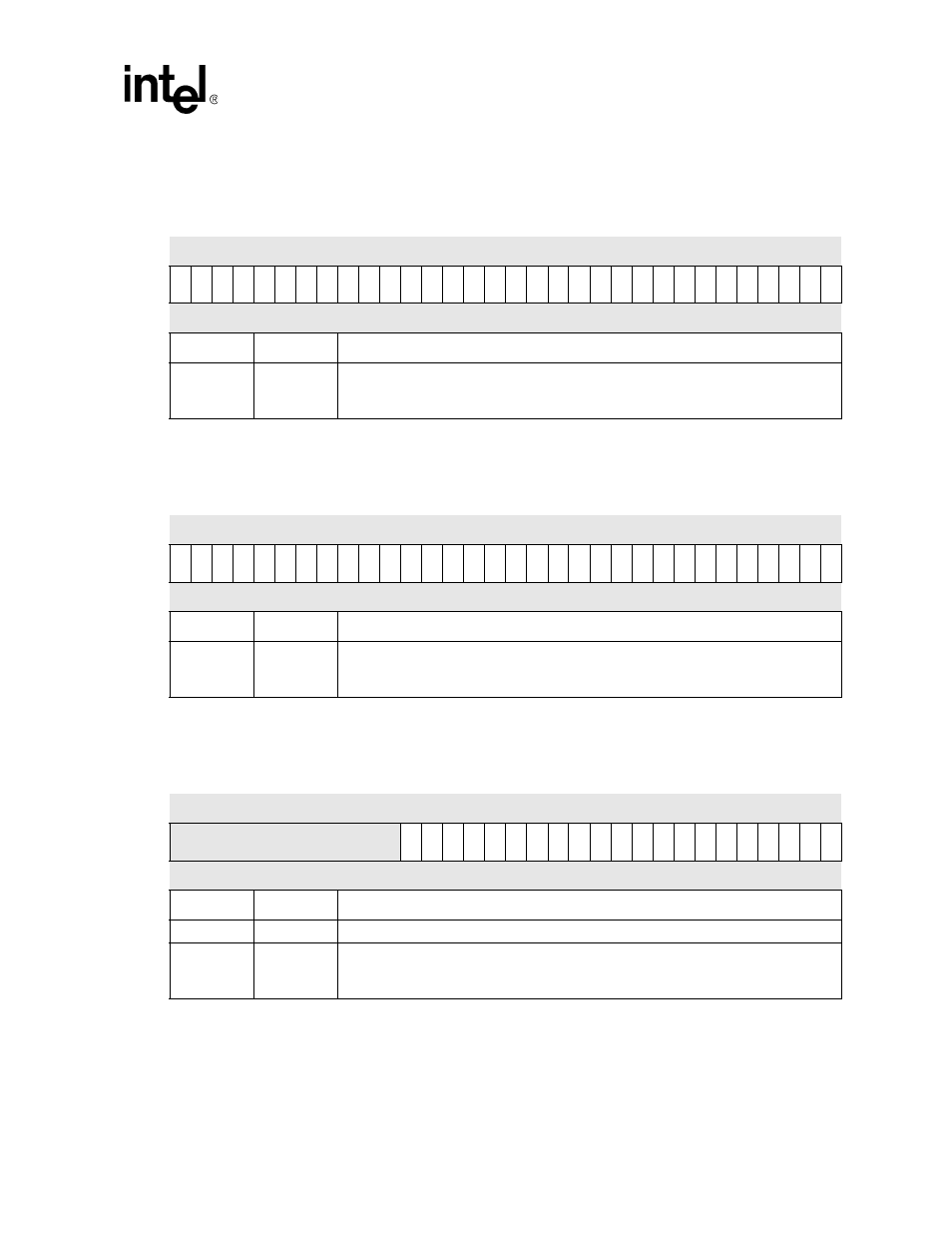

Table 4-6. GPDR0 Bit Definitions

Physical Address

0x40E0_000C

GPDR0

System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

PD

3

1

PD

3

0

PD

2

9

PD

2

8

PD

2

7

PD

2

6

PD

2

5

PD

2

4

PD

2

3

PD

2

2

PD

2

1

PD

2

0

PD

1

9

PD

1

8

PD

1

7

PD

1

6

PD

1

5

PD

1

4

PD

1

3

PD

1

2

PD1

1

PD

1

0

PD

9

PD

8

PD

7

PD

6

PD

5

PD

4

PD

3

PD

2

PD

1

PD

0

Reset 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

<31:0>

PD[x]

GPIO Pin ‘x’ Direction (where x = 0 to 31).

0 – Pin configured as an input

1 – Pin configured as an output

Table 4-7. GPDR1 Bit Definitions

Physical Address

0x40E0_0010

GPDR1

System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

PD

6

3

PD

6

2

PD

6

1

PD

6

0

PD

5

9

PD

5

8

PD

5

7

PD

5

6

PD

5

5

PD

5

4

PD

5

3

PD

5

2

PD

5

1

PD

5

0

PD

4

9

PD

4

8

PD

4

7

PD

4

6

PD

4

5

PD

4

4

PD

4

3

PD

4

2

PD

4

1

PD

4

0

PD

3

9

PD

3

8

PD

3

7

PD

3

6

PD

3

5

PD

3

4

PD

3

3

PD

3

2

Reset 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

<31:0>

PD[x]

GPIO Pin ‘x’ Direction (where x = 32 to 63).

0 – Pin configured as an input.

1 – Pin configured as an output.

Table 4-8. GPDR2 Bit Definitions

Physical Address

0x40E0_0014

GPDR2

System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

PD

8

4

PD

8

3

PD

8

2

PD

8

1

PD

8

0

PD

7

9

PD

7

8

PD

7

7

PD

7

6

PD

7

5

PD

7

4

PD

7

3

PD

7

2

PD

7

1

PD

7

0

PD

6

9

PD

6

8

PD

6

7

PD

6

6

PD

6

5

PD

6

4

Reset 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

<31:21>

—

reserved

<20:0>

PD[x]

GPIO Pin ‘x’ Direction (where x = 64 to 84).

0 – Pin configured as an input.

1 – Pin configured as an output