9 clocks and power manager register summary, 1 clocks manager register locations, 2 power manager register summary – Intel PXA255 User Manual

Page 103: Clocks manager register locations -41, Power manager register summary -41, Clocks manager register summary -41

Intel® PXA255 Processor Developer’s Manual

3-41

Clocks and Power Manager

3.8.3

Driving the Crystal Pins from an External Clock Source

The information in this section is provided as a guideline. The electrical specifications for the

crystal oscillator pins are in Intel® PXA255 Processor Electrical, Mechanical, and Thermal

Specification.

A 3.6864 MHz crystal must be connected between the PXTAL and PEXTAL pins. A 32.768 kHz

crystal is normally connected between the TXTAL and TEXTAL pins. This configuration gives the

lowest overall power consumption because the crystal’s resonant nature provides better power

efficiency than an external source that drives the crystal pins. Some applications have other clock

sources of the same frequency and can reduce overall cost by driving the crystal pins externally.

Refer to the Oscillator Electrical Specifications in the Intel® PXA255 Processor Design Guide for

more information.

Note: No external capacitors are required.

3.8.4

Noise Coupling Between Driven Crystal Pins and a Crystal

Oscillator

The two pairs of crystal pins are located near each other on the processor. When crystal oscillators

are connected to the pins, this proximity leads to low signal swings and slow edges that result in

limited noise coupling between the pins. If one of the crystal oscillators is replaced by an

independent signal source and the other is not, the noise coupling may increase. To limit this effect,

reduce the slew rate on the pins driven by the independent source.

3.9

Clocks and Power Manager Register Summary

3.9.1

Clocks Manager Register Locations

shows the registers associated with the clocks manager and the physical addresses used

to access them.

3.9.2

Power Manager Register Summary

shows the registers associated with the PM and the physical addresses used to access

them.

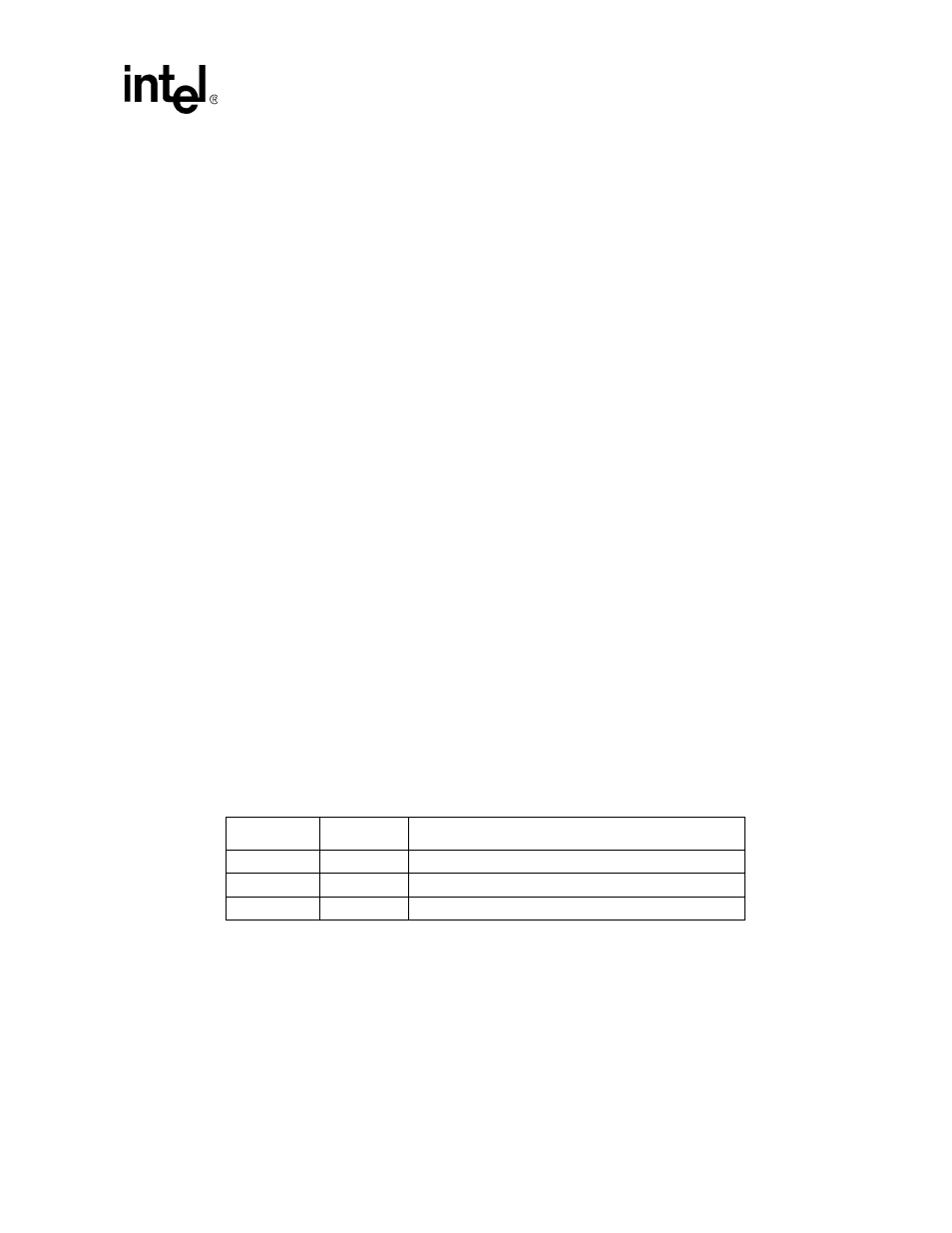

Table 3-26. Clocks Manager Register Summary

Address

Name

Description

0x4130_0000

CCCR

Core Clock Configuration Register

0x4130_0004

CKEN

Clock Enable Register

0x4130_0008

OSCC

Oscillator Configuration Register