Figure 6-27 – Intel PXA255 User Manual

Page 249

Intel® PXA255 Processor Developer’s Manual

6-67

Memory Controller

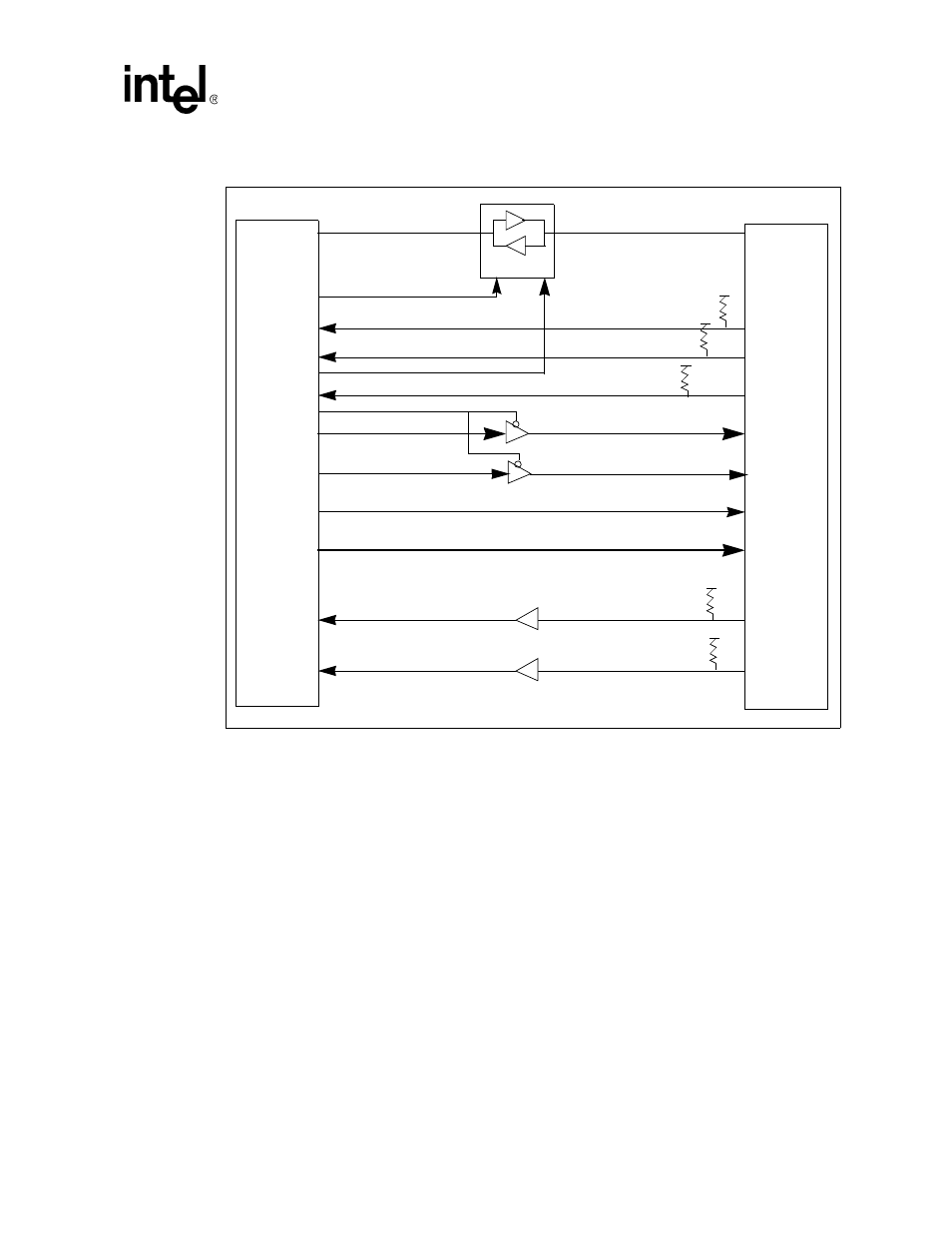

shows the glue logic need for a 2-socket system. RDY/nBSY signals are routed

through a buffer to two separate GPIO pins. In the data bus transceiver control logic, nPCE1

controls the enable for the low byte lane and nPCE2 controls the enable for the high byte lane.\

Figure 6-27. Expansion Card External Logic for a One-Socket Configuration

MD<15:0>

D<15:0>

nOE

DIR

nCD<1>

nCD<2>

RDY/nBSY

A[25:0]

nREG

nCE<2:1>

nOE

nWE

nIOR

nIOW

nWAIT

nIOIS16

GPIO

GPIO

MA[25:0]

nPREG

nPOE

nPWE

nPIOR

nPIOW

nPWAIT

nIOIS16

nPCE<2:1>

GPIO

PSKTSEL

RD/nWR

GPIO

Intel® - PXA255 Processor

Socket 0

nPCD0

nPCD1

PRDY_BSY0

PADDR_EN0

5V to 3.3V or 2.5V

5V to 3.3V or 2.5V