2 bits per pixel data memory organization -12, 4 bits per pixel data memory organization -12, 8 bits per pixel data memory organization -12 – Intel PXA255 User Manual

Page 276

7-12

Intel® PXA255 Processor Developer’s Manual

LCD Controller

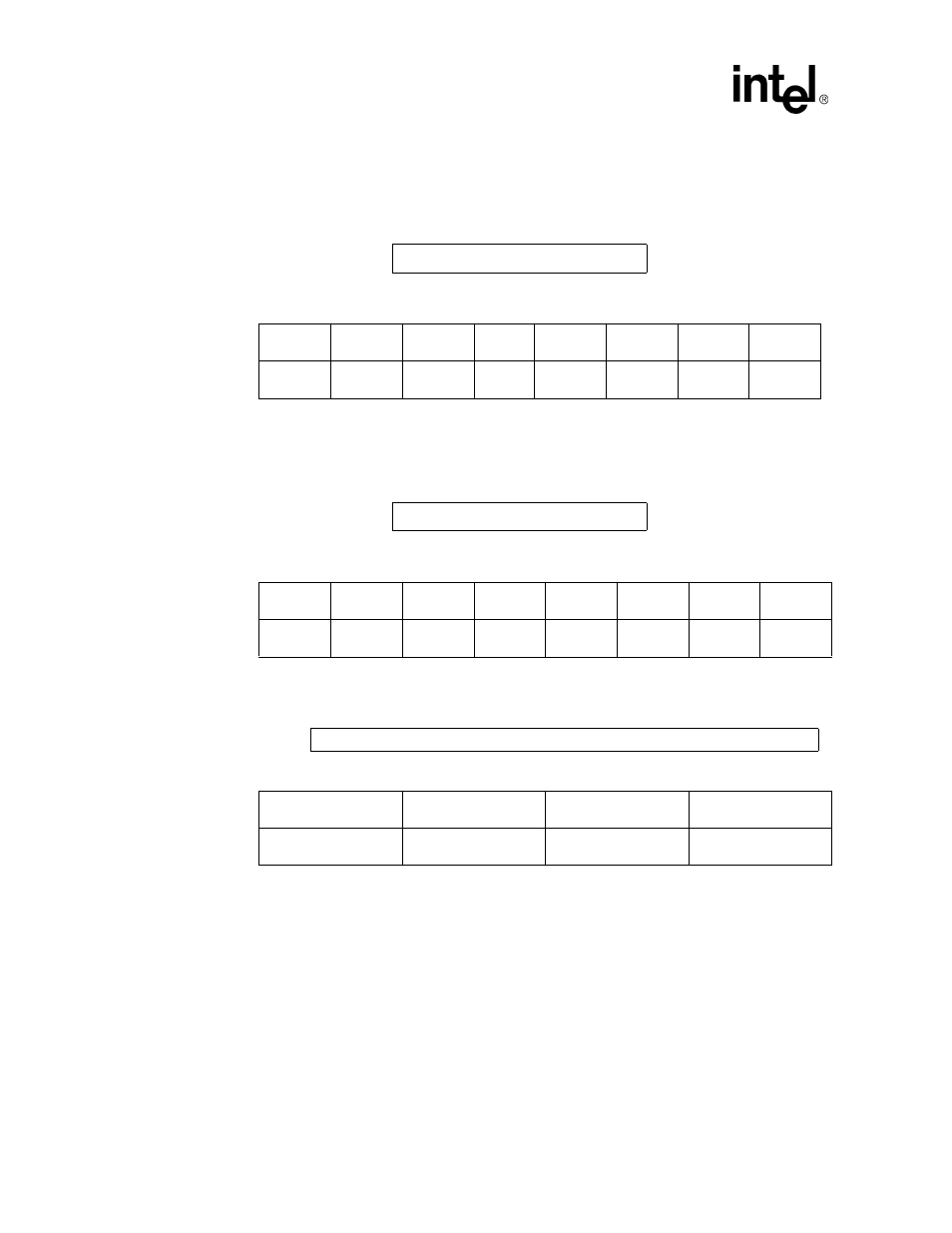

Figure 7-7. 2 Bits Per Pixel Data Memory Organization

Figure 7-8. 4 Bits Per Pixel Data Memory Organization

Figure 7-9. 8 Bits Per Pixel Data Memory Organization

Bit

1

0

2 bits/pixel

Palette Buffer Index<1:0>

Bit

31

30

29

28

27

26

...

7

6

5

4

3

2

1

0

Base

+ 0x0

Pixel 15

Pixel 14

Pixel 13

...

Pixel 3

Pixel 2

Pixel 1

Pixel 0

Base

+ 0x4

Pixel 31

Pixel 30

Pixel 29

...

Pixel 19

Pixel18

Pixel 17

Pixel 16

Bit

3

2

1

0

4 bits/pixel

Palette Buffer Index<3:0>

Bit

31

28

27

24

23

20

19

16

15

12

11

8

7

4

3

0

Base

+ 0x0

Pixel 7

Pixel 6

Pixel 5

Pixel 4

Pixel 3

Pixel 2

Pixel 1

Pixel 0

Base

+ 0x4

Pixel 15

Pixel 14

Pixel 13

Pixel 12

Pixel 11

Pixel 10

Pixel 9

Pixel 8

Bit

7

6

5

4

3

2

1

0

8 bits/pixel

Palette Buffer Index<7:0>

Bit

31

24

23

16

15

8

7

0

Base

+ 0x0

Pixel 3

Pixel 2

Pixel 1

Pixel 0

Base

+ 0x4

Pixel 7

Pixel 6

Pixel 5

Pixel 4