2 mmc_status register (mmc_stat), 2 mmc_status register (mmc_stat) -23, Mmc_strpcl bit definitions -23 – Intel PXA255 User Manual

Page 527: Mmc_stat bit definitions -23, Table 15-5

Intel® PXA255 Processor Developer’s Manual

15-23

MultiMediaCard Controller

15.5.2

MMC_Status Register (MMC_STAT)

MMC_STAT, shown in

, is the status register for the MMC controller. The register is

cleared at the beginning of every command sequence.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

Table 15-5. MMC_STRPCL Bit Definitions

Physical Address

0x4110_0000

MMC_STRPCL Register

MultiMediaCard Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

ST

RP

CL

Reset 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description

31:2

—

reserved

1:0

strpcl

Start/Stop the MMC Clock

00 – Do nothing

01 – Stop the MMC clock

10 – Start the MMC clock

11 – reserved

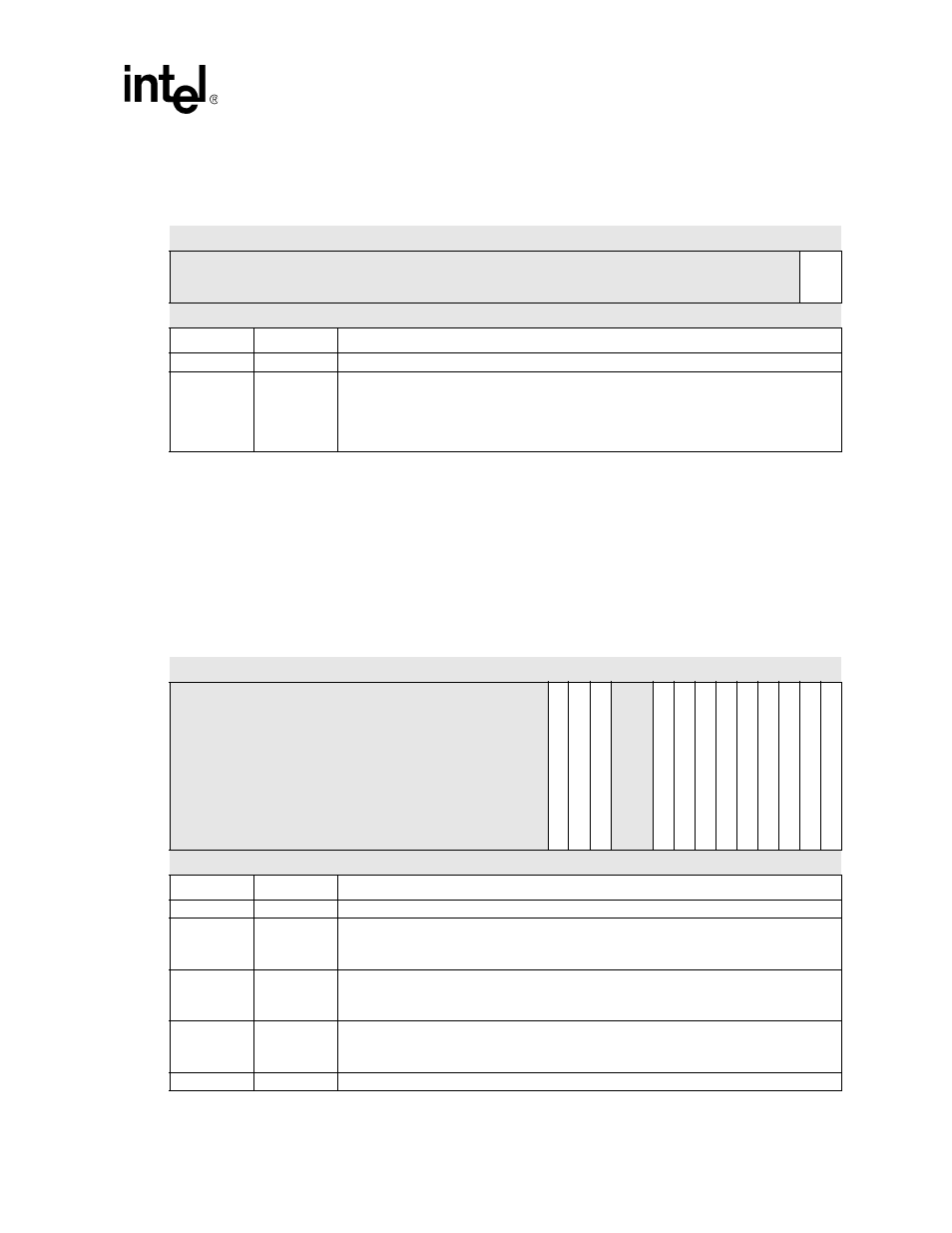

Table 15-6. MMC_STAT Bit Definitions (Sheet 1 of 2)

Physical Address

0x4110_0004

MMC_STAT Register

MultiMediaCard Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

EN

D_

C

M

D_

RE

S

PRG

_

DO

NE

DA

TA

_

T

R

A

N

_

DO

NE

re

ser

ved

CL

K

_

EN

R

E

C

V

_FIFO

_

FU

LL

XM

IT

_F

IF

O

_

E

M

PT

Y

RE

S

_

CR

C_

E

R

R

SPI_

R

EA

D_

ER

RO

R_

TO

K

E

N

C

R

C

_

RE

AD

_E

RR

OR

CR

C_

W

R

IT

E_

ER

RO

R

TIM

E

_

O

UT_

R

ESP

O

N

SE

REA

D

_

T

IM

E_

O

U

T

Reset 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

Bits

Name

Description

31:14

—

reserved

13

END_CMD_R

ES

End Command Response

0 – Command and response sequence has not completed

1 – Command and response sequence has completed

12

PRG_DONE

Program Done

0 – Card has not finished programming and is busy

1 – 1 = Card has finished programming and is not busy

11

DATA_TRAN_

DONE

Data Transmission Done

0 – Data transmission to card has not completed

1 – Data transmission to card has completed

10:9

—

reserved