4 psp details, Figure 16-8, Figure 16-7 – Intel PXA255 User Manual

Page 552

16-10

Intel® PXA255 Processor Developer’s Manual

Network SSP Serial Port

Note: When configured master the SSP continues to drive SSPTXD with the last bit of data sent (the

LSB) or it drives zero, depending on the status of SSPSP[ETDS]. If SSCR0[SSE] is cleared,

SSPTXD goes low. The state of SSPRXD is undefined before the MSB and after the LSB is

transmitted. For minimum power consumption, this pin must not float.

Note: When configured master the SSP continues to drive SSPTXD with the last bit of data sent (the

LSB) or it drives zero, depending on the status of SSPSP[ETDS]. If SSCR0[SSE] is cleared,

SSPTXD goes low. The state of SSPRXD is undefined before the MSB and after the LSB is

transmitted. For minimum power consumption, this pin must not float.

16.4.3.4

PSP Details

The PSP provides programmability for several parameters that determine the transfer timings

between data.

There are four possible serial clock sub-modes, depending on the SSPSCLK edges selected for

driving data and sampling received data and the selection of idle state of the clock.

For the PSP, the idle and disable modes of the SSPTXD, SSPSCLK, and SSPSFRM are

programmable via SSPSP[ETDS], SSPSP[SCMODE] and SSPSP[SFRMP]. When transmit data is

ready, the SSPSCLK remains in its idle state for the number of serial clock (SSPSCLK) clock

periods programmed within the start delay (SSPSP[STRTDLY]) field. SSPSCLK then starts

toggling, SSPTXD remains in the idle state for the number of cycles programmed within the

dummy start field (SSPSP[DMYSTRT]). The SSPSFRM signal asserts after the number of half-

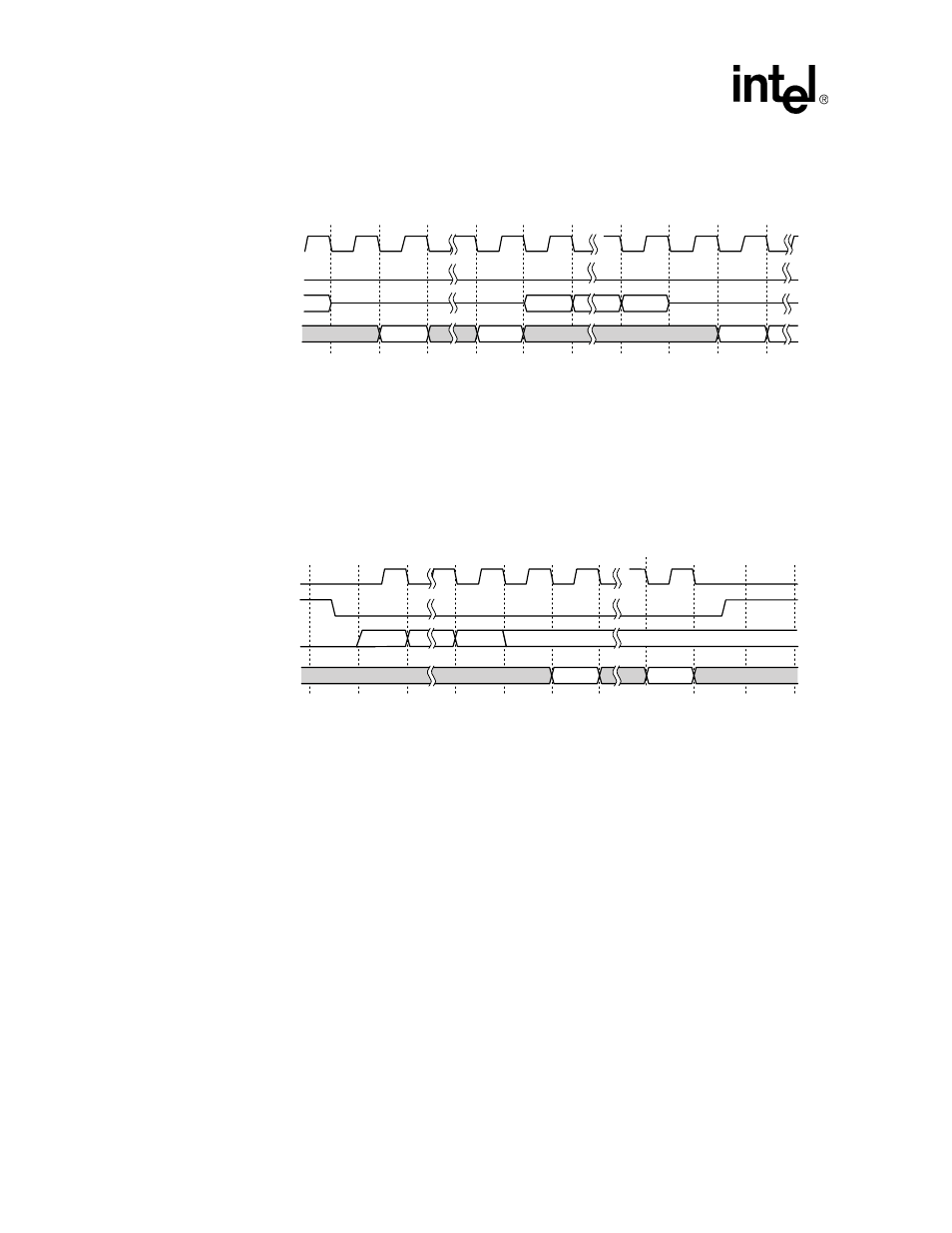

Figure 16-7. National Semiconductor Microwire

*

Frame Protocol (multiple transfers)

Figure 16-8. National Semiconductor Microwire

*

Frame Protocol (single transfers)

A9653-01

SSPSCLK

SSPSFRM

SSPTX/RX

Bit[0]

Bit[7] or

Bit[15]

Bit[0]

Bit[1]

SSPTX/RX

Bit[N]

Bit[0]

Bit[N]

Undefined

Undefined

Undefined

A9521-02

SSPRXD

SSPSFRM

SSPSCLK

SSPTXD

4 to 32 Bits

Bit[7] or

Bit[15]

8 or 16-Bit Control

Bit[0]

Bit[N]

Bit[0]

End of Transfer Data State

Undefined

Undefined

Undefined