Intel PXA255 User Manual

Page 164

5-14

Intel® PXA255 Processor Developer’s Manual

DMA Controller

5.2.3

Servicing Companion Chips and External Peripherals

Companion chips and external peripherals can be serviced with flow-through transfers. The

DMAC provides DMA Request to Channel Map Registers (DRCMRx) that contain four bits that

assign a channel number for each of the possible DMA requests. The companion-chip requests are

DREQ[1:0]. The DREQ signal can be mapped to one of the 16 available channels. The DREQ

signals are sampled on every peripheral clock (PCLK) and if any of the DREQ signals are sampled

non-zero, a lookup is performed on the corresponding bits in the DRCMRx. This allows requests to

one of the channels to be mapped. If the external peripheral address is in the DSADR, the

DCMDx[FLOWSRC] bit must be set to a 1. If the external peripheral address is in the DTADR, the

DCMDx[FLOWTRG] bit must be set to a 1. This allows the processor to wait for the request

before it initiates the transfer.

If DCMDx[IRQEN] is set to a 1, a DMA interrupt can be requested at the end of the last cycle

associated with the byte that caused DCMDx[LENGTH] to decrease from a 1 to a 0.

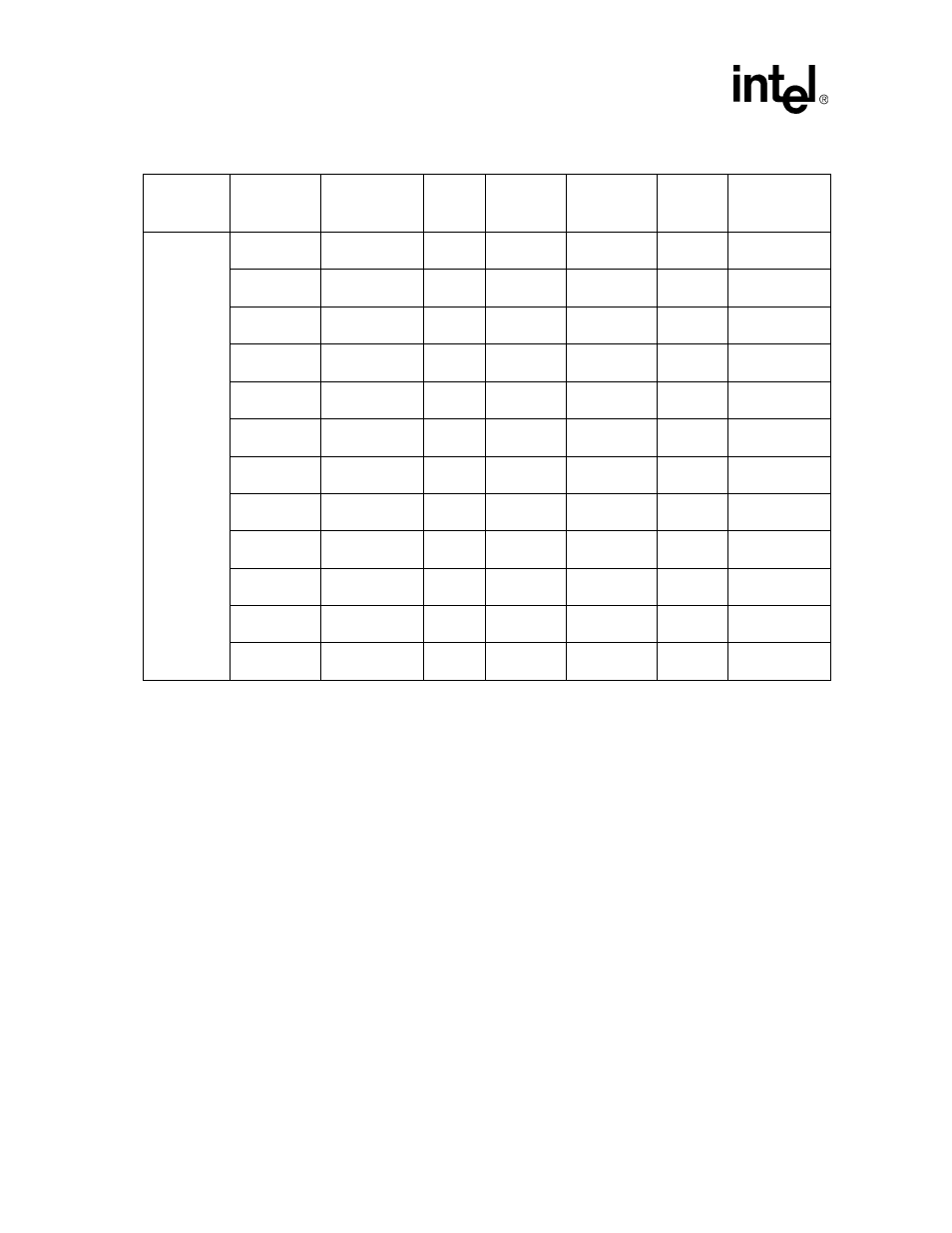

USB

endpoint 1

transmit

0x4060_0100

1

01

32

Target

0x4000_0164

endpoint 2

receive

0x4060_0180

1

01

32

Source

0x4000_0168

endpoint 3

transmit

0x4060_0200

1

01

32

Target

0x4000_016C

endpoint 4

receive

0x4060_0400

1

01

32

Source

0x4000_0170

endpoint 6

transmit

0x4060_0600

1

01

32

Target

0x4000_0178

endpoint 7

receive

0x4060_0680

1

01

32

Source

0x4000_017C

endpoint 8

transmit

0x4060_0700

1

01

32

Target

0x4000_0180

endpoint 9

receive

0x4060_0900

1

01

32

Source

0x4000_0184

endpoint 11

transmit

0x4060_0B00

1

01

32

Target

0x4000_018C

endpoint 12

receive

0x4060_0B80

1

01

32

Source

0x4000_0190

endpoint 13

transmit

0x4060_0C00

1

01

32

Target

0x4000_0194

endpoint 14

receive

0x4060_0E00

1

01

32

Source

0x4000_0198

Table 5-5. DMA Quick Reference for Internal Peripherals (Sheet 2 of 2)

Unit

Function

FIFO Address

Width

(bytes)

DCMD.

Width

(binary)

Burst Size

(bytes)

Source

or

Target

DRCMR