Mdrefr bit definitions -15 – Intel PXA255 User Manual

Page 197

Intel® PXA255 Processor Developer’s Manual

6-15

Memory Controller

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

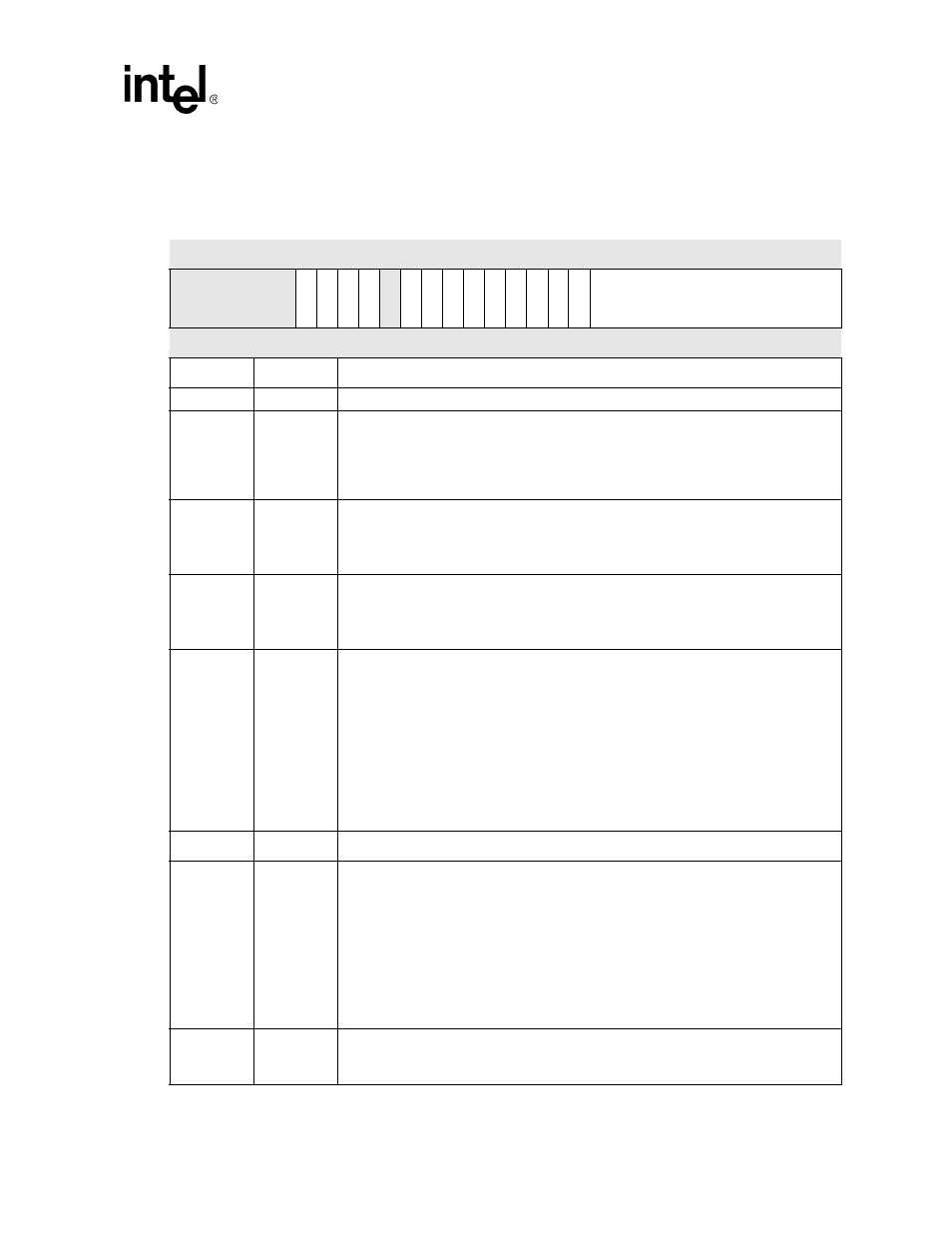

Table 6-5. MDREFR Bit Definitions (Sheet 1 of 3)

0x4800_0004

MDREFR

Memory Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

K2

F

R

EE

K1

F

R

EE

K0

F

R

EE

SLFR

S

H

re

ser

ve

d

AP

D

K2

D

B

2

K2

RU

N

K1

D

B

2

K1

RU

N

E1

P

IN

K0

D

B

2

K0

RU

N

E0

P

IN

DRI

Reset 0

0

0

0

0

0

1

1

1

1

0

0

1

0

1

0

0

1

*

*

1

1

1

1

1

1

1

1

1

1

1

1

Bits

Name

Description

31:26

—

reserved

25

K2FREE

SDRAM Free-Running Control

0 – SDCLK2 is not free-running

1 – SDCLK2 is free-running (ignores MDREFR[APD] or MDREFR[K2RUN] bits)

Provides synchronous memory with SDCLK2 following a reset in order to reset internal

circuitry.

24

K1FREE

SDRAM Free-Running Control

0 – SDCLK1 is not free-running

1 – SDCLK1 is free-running (ignores MDREFR[APD] or MDREFR[K1RUN] bits)

Provides synchronous memory with SDCLK1 following a reset to reset internal circuitry.

23

K0FREE

SDRAM Free-Running Control

0 – SDCLK0 is not free-running

1 – SDCLK0 is free-running (ignores MDREFR[APD] or MDREFR[K0RUN] bits)

Provides synchronous memory with SDCLK0 following a reset to reset internal circuitry.

22

SLFRSH

SDRAM Self-Refresh Control/Status

Control/status bit for entering and exiting SDRAM self-refresh and is automatically set on a

hardware or sleep reset.

0 – Self refresh disabled

1 – Self refresh enabled

SLFRSH can be set by software to force a self-refresh command. E1PIN does not have to

be cleared. The appropriate clock run bits (K1RUN and/or K2RUN) must remain set until

SDRAM has entered self-refresh and must be set prior to exiting self-refresh (clearing

SLFRSH). This capability must be used with extreme caution because the resulting state

prohibits automatic transitions for any commands.

Clearing SLFRSH is a part of the hardware or sleep reset procedure for SDRAM.

21

—

reserved

20

APD

SDRAM/Synchronous Static Memory Auto-Power-Down Enable.

If APD=1, the clock enables and clock pins are automatically deasserted when none of the

corresponding partitions are being accessed unless the KxFREE bits are set.

If no SDRAM partitions are being accessed, the SDRAM chips are put into Power-Down

mode and the clocks and clock-enable pins are turned off.

If one SDRAM partition is being used and the other is not, the clock to the partition that is

not being used are turned off.

If no Synchronous Static Memory partitions are being used, the clock and clock enable to

these partitions are turned off and the memory chips are put into Power-Down mode. See

19

K2DB2

SDRAM Clock Pin 2 (SDCLK2) Divide by 2 Control/Status

0 – SDCLK2 is same frequency as MEMCLK

1 – SDCLK2 runs at one-half the MEMCLK frequency