Intel PXA255 User Manual

Page 175

Intel® PXA255 Processor Developer’s Manual

5-25

DMA Controller

18

ENDIAN

Device Endian-ness. (read / write).

0 – Byte ordering is little endian

1 – reserved

17:16

SIZE

Maximum Burst Size of each data transferred (read / write).

00 – reserved

01 – 8 Bytes

10 – 16 Bytes

11 – 32 Bytes

If DCMDx[LENGTH] is less than DCMDx[SIZE] the data transfer size equals

DCMDx[LENGTH].

15:14

WIDTH

Width of the on-chip peripheral. (read / write/).

00 – reserved

01 – 1 byte

10 – HalfWord (2 bytes)

11 – Word (4 Bytes)

Must be programmed 00 for memory-to-memory moves or companion-chip related

operations.

13

—

reserved

12:0

LENGTH

Length of transfer in bytes. (read / write).

Indicates the length of transfer in bytes. DCMD[LENGTH] = 0 means zero bytes for

Descriptor Fetch Mode only. DCMD[LENGTH] = 0 is an invalid setting for the No-Descriptor

Fetch Mode. The maximum transfer length is (8K-1) bytes. If the transfer involves any of

the internal peripherals, the length of the transfer must be an integer multiple of the width of

that peripheral.

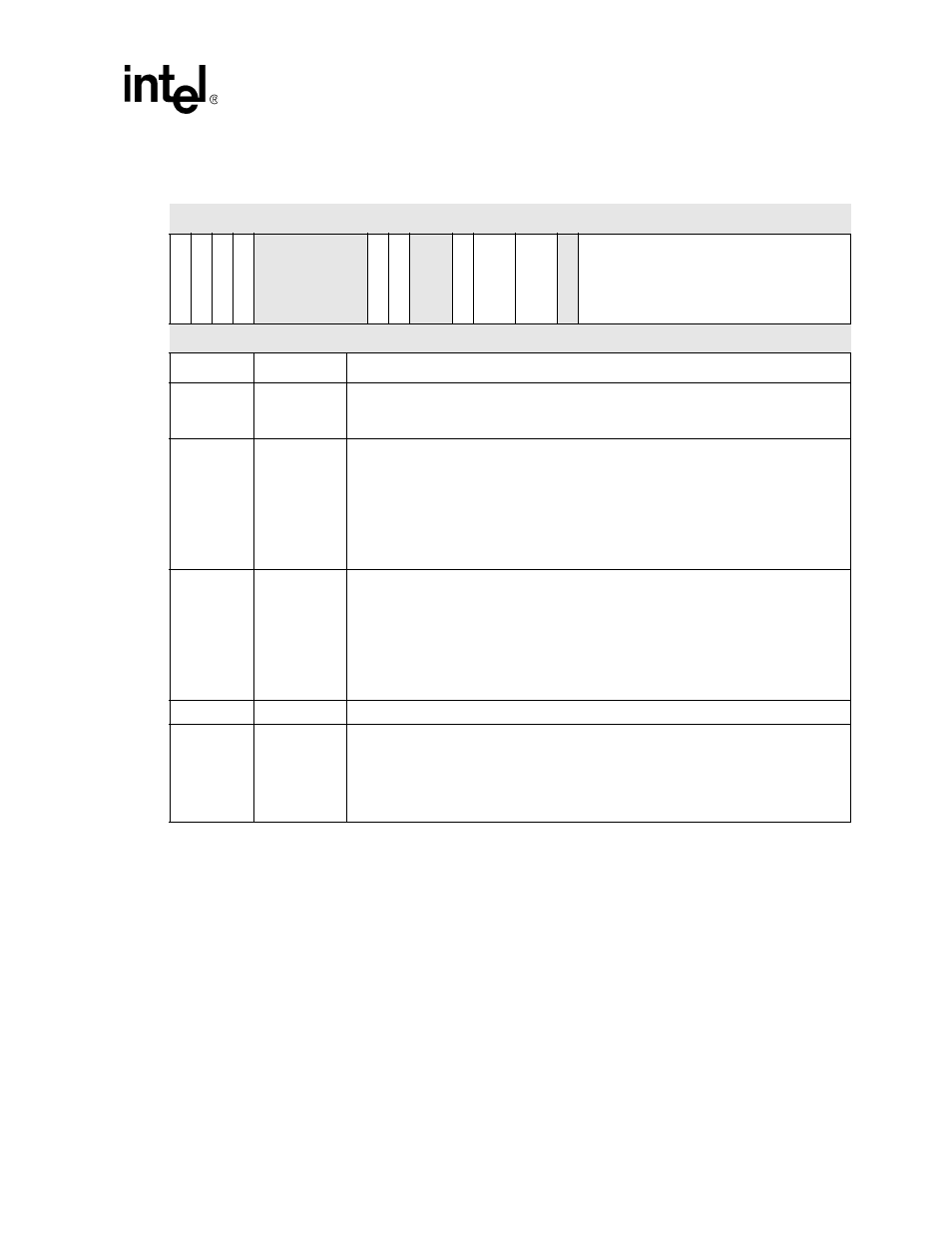

Table 5-12. DCMDx Bit Definitions (Sheet 2 of 2)

0x4000_02xC

DMA Command Register (DCMDx)

DMA Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

IN

CS

RC

AD

DR

IN

CT

R

G

AD

DR

FLO

W

SR

C

FLO

W

TR

G

reserved

S

TAR

T

IRQ

EN

EN

DI

R

Q

E

N

re

se

rv

e

d

EN

DIA

N

SIZE

WID

T

H

re

se

rv

e

d

LENGTH

Reset 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bits

Name

Description