7 ssp data register (ssdr), 7 ssp data register (ssdr) -28 – Intel PXA255 User Manual

Page 570

16-28

Intel® PXA255 Processor Developer’s Manual

Network SSP Serial Port

16.5.7

SSP Data Register (SSDR)

SSDR, shown in

, is a single address location that read and write data transfers access.

SSDR represents two physical registers: the first is temporary storage for data on its way out

through the transmit FIFO. The other register is temporary storage for data coming in through the

receive FIFO.

5

TFS

TRANSMIT FIFO SERVICE REQUEST:

Indicates that the transmit FIFO requires service to prevent an underrun. TFS is set when the

number of valid entries in the transmit FIFO is equal to or lesser than the transmit FIFO trigger

threshold. It is cleared when it has fewer entries than the trigger threshold value. When TFS is

set, an Interrupt is generated when SSCR1[TIE] is set. Setting TFS signals a DMA service

request if SSCR1[TSRE] is set. After the CPU or DMA fills the FIFO such that it has at least as

many entries as the value of SSCR1[TFT], TFS (and the service request or interrupt) is

automatically cleared. SSCR1[TSRE] and SSCR1[TIE] must not both be set.

0 – Transmit FIFO level exceeds TFT trigger threshold or the SSP is disabled

1 – Transmit FIFO level is at or below TFT trigger threshold, request Interrupt

4

BSY

SSP BUSY:

Indicates that the port is actively transmitting or receiving data and is cleared when the port is

idle or disabled. This bit does not generate an Interrupt. Software must wait for the Tx Fifo to

empty first and then wait for the BSY bit to be cleared at the end of a data transfer.

0 – SSP is idle or disabled

1 – SSP currently transmitting or receiving a frame

3

RNE

RECEIVE FIFO NOT EMPTY:

Indicates that the receive FIFO contains one or more entries of valid data. It is cleared when it no

longer contains any valid data. This bit does not generate an Interrupt.

When using programmed I/O, this bit can be polled to remove remaining bytes of data from the

receive FIFO since CPU Interrupt requests are made only when the receive FIFO trigger

threshold has been met or exceeded.

0 – Receive FIFO is empty.

1 – Receive FIFO is not empty.

2

TNF

TRANSMIT FIFO NOT FULL:

Indicates that the transmit FIFO contains one or more entries that do not contain valid data. TNF

is cleared when the FIFO is completely full. This bit does not generate an Interrupt.

When using programmed I/O, this bit can be polled to fill the transmit FIFO over its trigger

threshold.

0 – Transmit FIFO is full

1 – Transmit FIFO is not full

1:0

—

reserved

Table 16-8. SSSR Bit Definitions (Sheet 3 of 3)

0x4140_0008

SSSR

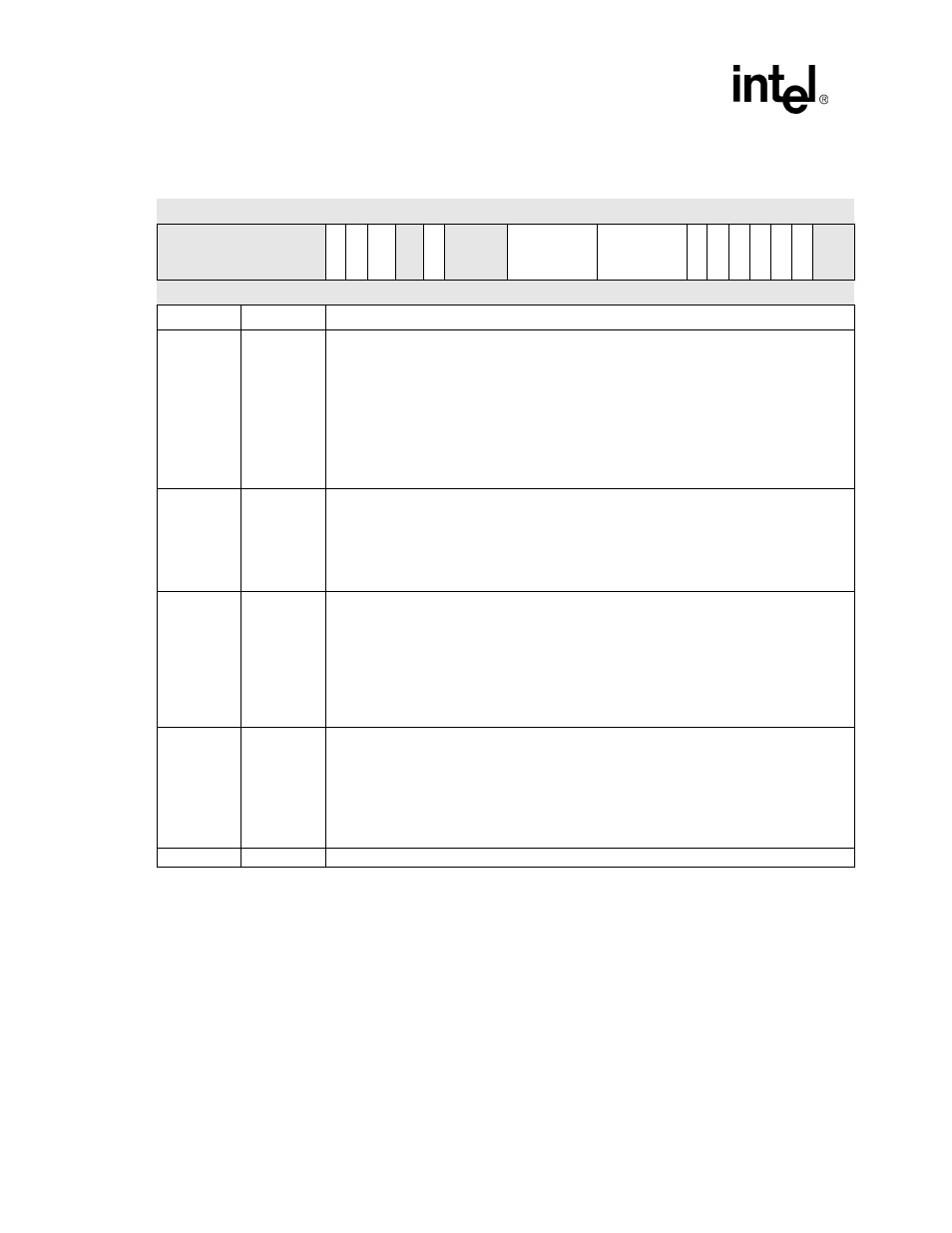

Network SSP Serial Port

Bit

31 30 29 28 27 26 25 24 23 22 21

20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

reserved

BC

E

CS

S

TU

R

reser

ve

d

TIN

T

reser

ve

d

RF

L

TFL

RO

R

RF

S

TFS

BS

Y

RN

E

TN

F

reser

ve

d

Reset ? ? ? ? ? ? ? ?

0

0

0

?

0 ? ? ?

1 1

1

1

0

0

0

0

0

0

0

0

0

1

? ?

Bits

Name

Description