Comtech EF Data DM240XR User Manual

Page 125

DM240XR High-Speed Digital Modulator

Remote Operations

MN-DM240XR– Revision 13

9–11

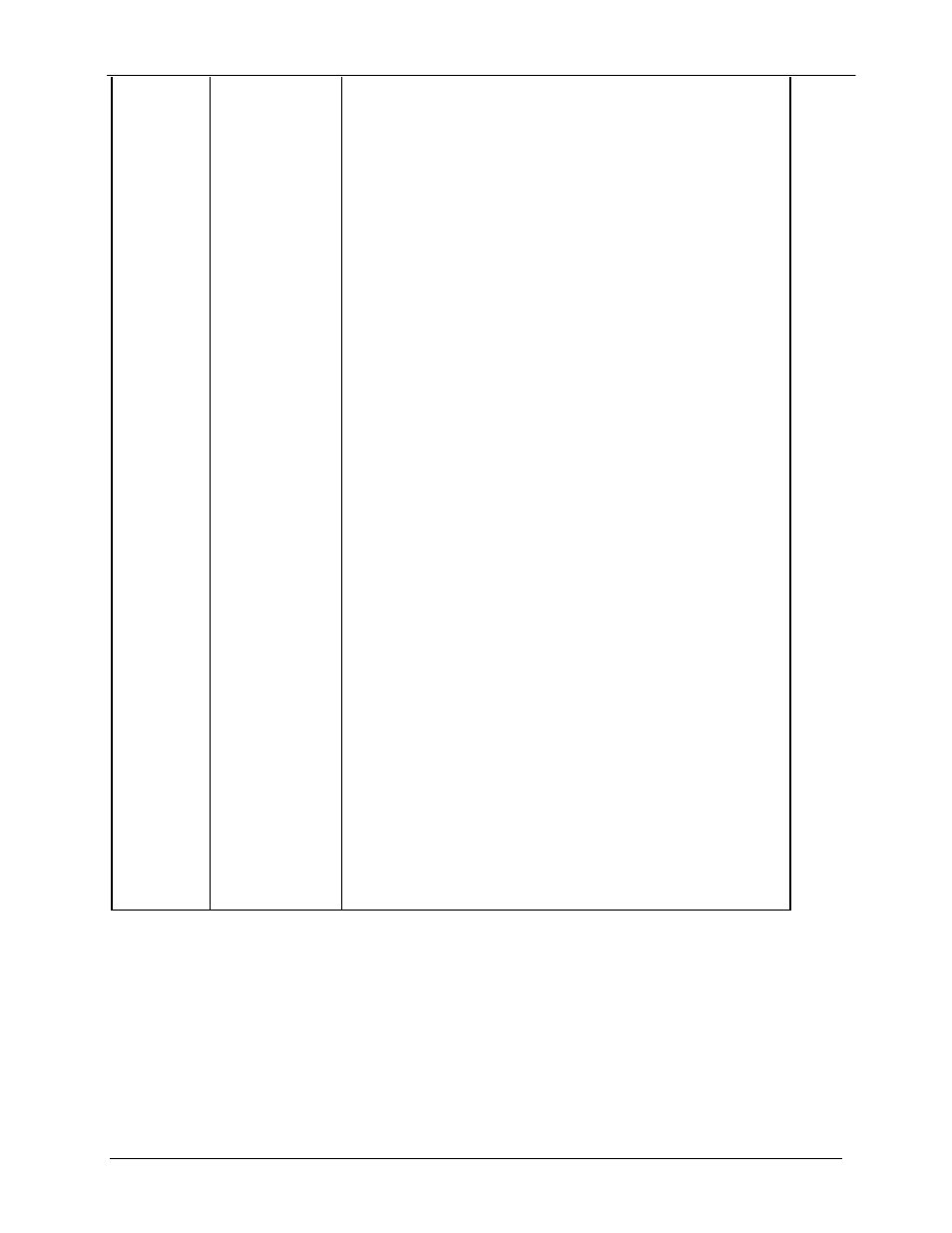

<1>

Latched Major

Alarm

Bit 0 = Spare

Bit 1 = Transmit Oversample PLL Lock

Bit 2 = FPGA Config Error

Bit 3 = IF Synthesizer PLL Lock

Bit 4 = External Reference PLL Lock

Bit 5 = Composite PLL Lock

Bit 6 = Symbol PLL Lock

Bit 7 = Spare

0 = Pass, 1 = Fail

<1>

Latched Minor

Alarm

Bit 0 = Terrestrial Ethernet data activity detect

Bit 1 = Loss Terrestrial Clock

Bit 2 = Loss Terrestrial Data

Bit 3 = FIFO Error

Bit 4 = Output Level

Bit 5 = Terrestrial Framing Error

Bit 6 = Terr Ethernet jitter buffer underflow

Bit 7 = Terr Ethernet jitter buffer overflow

0 = Pass, 1 = Fail

<1>

Latched

Common Fault

Bit 0 = -12 V Alarm

Bit 1 = +12 V Alarm

Bit 2 = +5 V Alarm

Bit 3 = Spare

Bit 4 = Spare

Bit 5 = Spare

Bit 6 = Spare

Bit 7 = Spare

0 = Pass, 1 = Fail

<1>

Reserved

TBD

<1>

+5 Voltage

+5 V. Implied Decimal Point. Ex: 49 = +4.9 V

<1>

+12 Voltage

+12 V. Implied Decimal Point. Ex: 121 = +12.1 V

<1>

-12 Voltage

-12 V. Implied Decimal Point and Minus Sign.

Ex: 118 = -11.8 V

<2>

Reserved

TBD

<2>

Reserved

TBD

<1>

Last Rate Status 0 = Symbol Rate, 1 = Data Rate

<1>

Active PIIC Slot 1 – 3