Zilog Z80380 User Manual

Page 44

5-10

Z380

™

U

SER

'

S

M

ANUAL

DC-8297-03

Z

ILOG

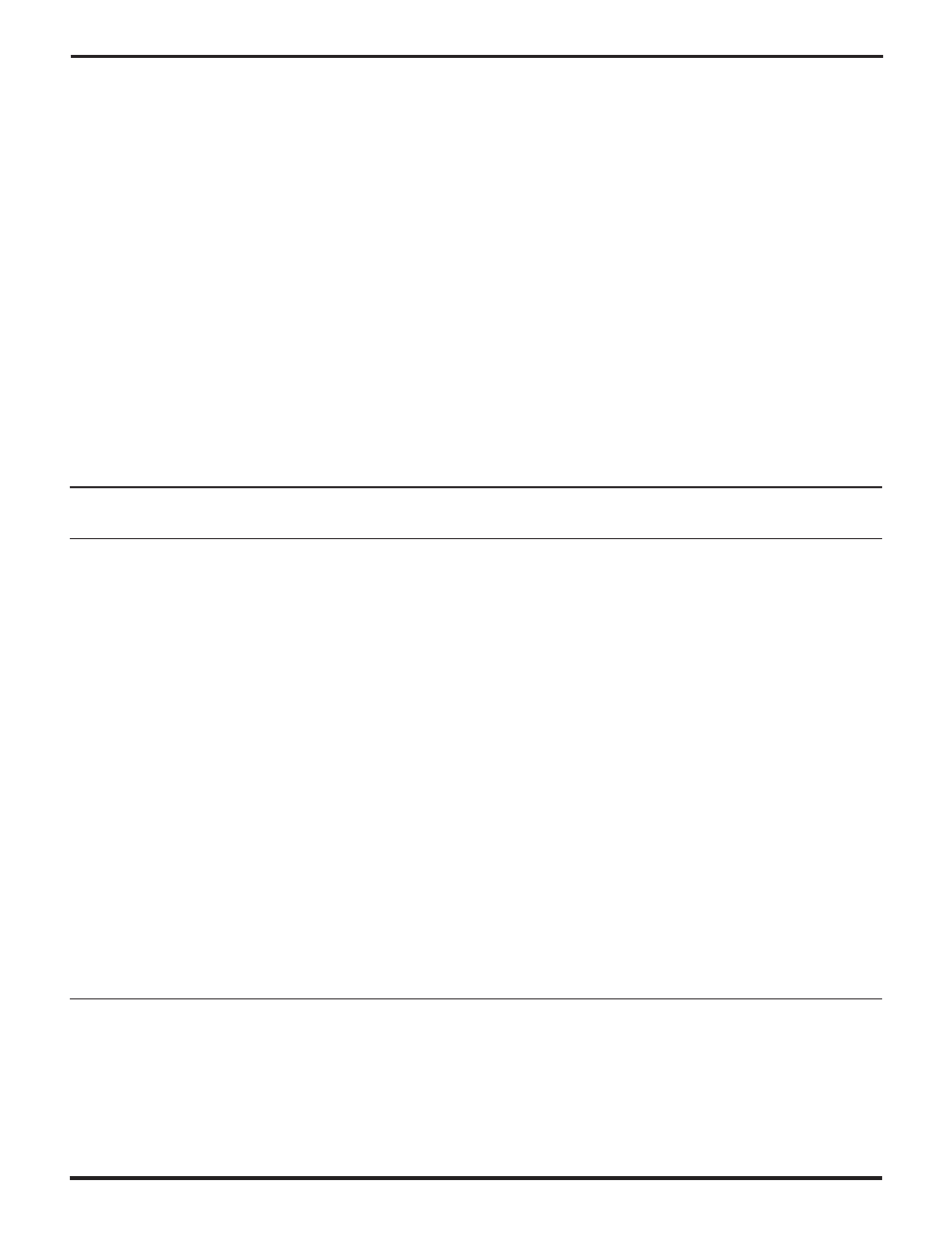

5.5.5 16-Bit Arithmetic Operation

This group of instructions (Table 5-10) provide 16-bit

arithmetic instructions. The Add, Add with Carry, Subtract,

Subtract with Carry, AND, OR, Exclusive OR, and Com-

pare takes one input operand from an addressing register

and the other from a 16-bit register, or from the instruction

itself; the result is returned to the addressing register. The

16-bit Increment and Decrement instructions operate on

data found in a register or in memory; the Indirect Register

or Direct Address addressing mode can be used to

specify the memory operand.

The remaining 16-bit instructions provide general arith-

metic capability using the HL register as one of the input

operands. The word Add, Subtract, Compare, and signed

and unsigned Multiply instructions take one input operand

from the HL register and the other from a 16-bit register,

from the instruction itself, or from memory using Indexed

Table 5-10. 16-Bit Arithmetic Operation

src/

Instruction Name

Format

dst

BC

DE

HL SP IX

IY nn (nn) (IX+d) (IY+d)

Add With Carry (Word)

ADC HL,src

src

√

√

√

√

ADCW [HL],src

src

√

√

√

√

√ √

√

√

Add (Word)

ADD HL,src

src

√

√

√

√

√

X

ADD IX,src

src

√

√

√

√

X

ADD IY,src

src

√

√

√

√

X

ADDW [HL,]src

src

√

√

√

√

√ √

√

√

Add to Stack Pointer

ADD SP,nn

src

√

X

AND Word

ANDW [HL,]src

src

√

√

√

√

√ √

√

√

Complement Accumulator

CPLW [HL]

dst

√

Compare (Word)

CPW [HL,]src

src

√

√

√

√

√ √

√

√

Decrement (Word)

DEC[W] dst

dst

√

√

√

√

√

√

X

Divide Unsigned

DIVUW [HL,]src

src

√

√

√

√

√ √

√

√

Extend Sign (Word)

EXTSW [HL]

dst

√

Increment (Word)

INC[W] dst

dst

√

√

√

√

√

√

X

Multiply Word Signed

MULT [HL,]src

src

√

√

√

√

√ √

√

√

Multiply Word Unsigned

MULTUW [HL,]src src

√

√

√

√

√ √

√

√

Negate Accumulator

NEGW [A]

dst

√

OR Word

ORW [HL,]src

src

√

√

√

√

√ √

√

√

Subtract with Carry (Word)

SBC HL,src

src

√

√

√

√

√

SBCW [HL],src

src

√

√

√

√

√ √

√

√

Subtract (Word)

SUB HL,(nn)

src

√

X

SUBW [HL,]src

src

√

√

√

√

√ √

√

√

Subtract from Stack Pointer

SUB SP,nn

src

√

X

Exclusive OR

XORW [HL,]src

src

√

√

√

√

√ √

√

√

Note:

that the instructions with “X” at the rightmost column is affected by

Extended mode. These operate across all the 32 bits in Modulo 2

32

for

address calculation.

or Direct Address addressing mode. The 32-bit result of a

multiply is returned to the HLz and HL (HL31-HL0). The

unsigned divide instruction takes a 16-bit dividend from

the HL register and a 16-bit divisor from a register, from the

instruction, or memory using the Indexed mode. The 16-bit

quotient is returned in the HL register and the 16-bit

reminder is returned to the HLz (HL31-HL16). The Extend

Sign instruction takes the contents of the HL register and

delivers the 32-bit result to the HLz and HL registers. The

Negate HL instruction negates the contents of the HL

register.

Except for Increment, Decrement, and Extend Sign, all the

instructions in this group set the CPU flags to reflect the

computed result.