Zilog Z80380 User Manual

Page 21

2-6

Z380

™

U

SER

'

S

M

ANUAL

DC-8297-03

Z

ILOG

2.5. EXTERNAL I/O ADDRESS SPACE

External I/O address space is 4 Gbytes in size and External

I/O addresses are generated by I/O instructions except

those reserved for on-chip I/O address space accesses. It

can take a variety of forms, as shown in Table 2.1. An

external I/O read or write is always one transaction, regard-

less of the bus size and the type of I/O instruction.

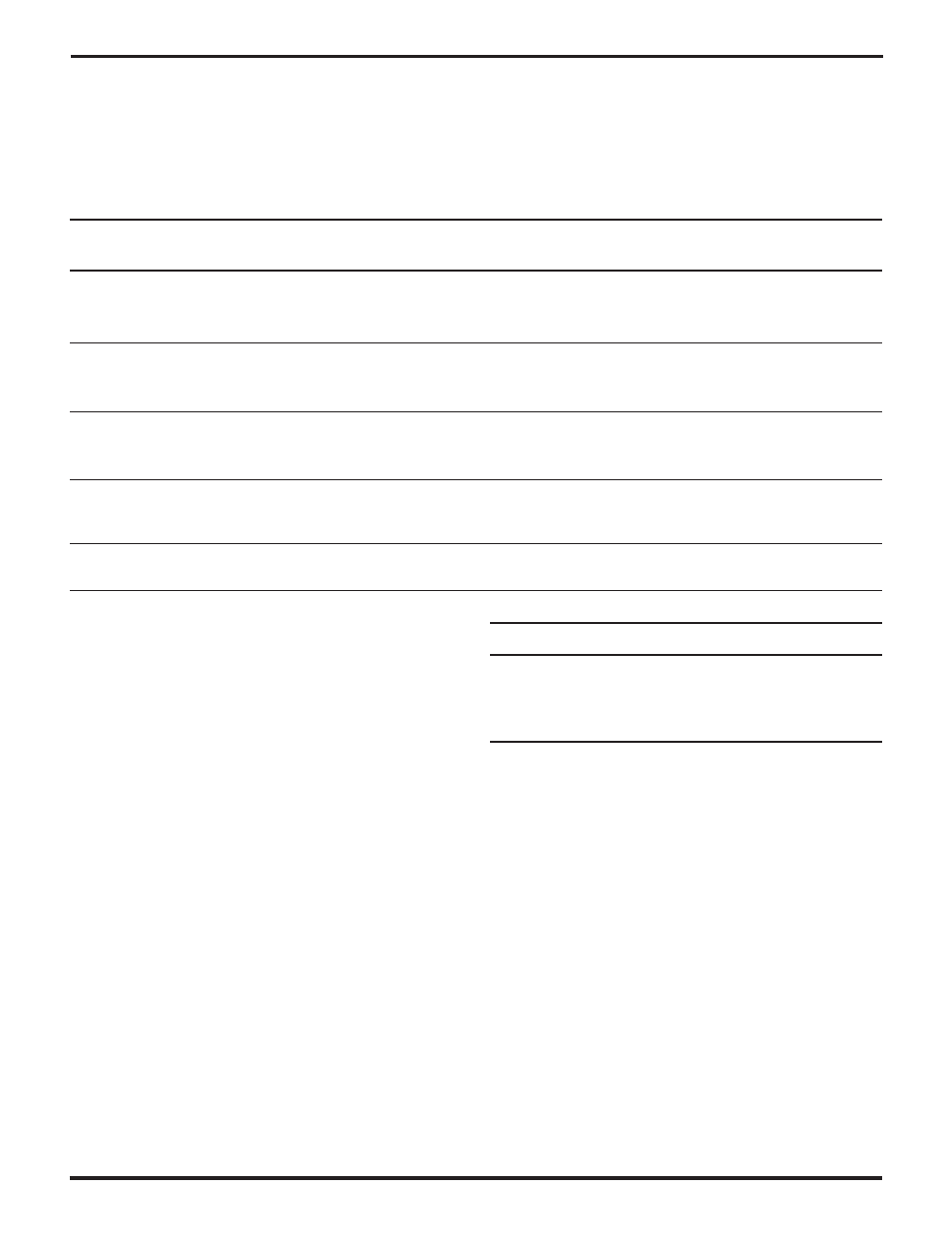

Table 2-1. I/O Addressing Options

Address Bus

I/O Instruction

A31-A24

A23-A16

A15-A8

A7-A0

IN A, (n)

00000000

00000000

A7-A0

n

IN dst,(C)

BC31-B24

BC23-B16

BC15-B8

BC7-B0

INA(W) dst,(mn)

00000000

00000000

m

n

DDIR IB INA(W) dst,(lmn)

00000000

l

m

n

DDIR IW INA(W) dst,(klmn)

k

l

m

n

Block Input

BC31-B24

BC23-B16

BC15-B8

BC7-B0

OUT (n),A

00000000

00000000

A7-A0

n

OUT (C),dst

BC31-B24

BC23-B16

BC15-B8

BC7-B0

OUTA(W) (mn),dst

00000000

00000000

m

n

DDIR IB OUTA(W) (lmn),dst

00000000

l

m

n

DDIR IW OUTA(W) (klmn),dst

k

l

m

n

Block Output

BC31-B24

BC23-B16

BC15-B8

BC7-B0

2.6. ON-CHIP I/O ADDRESS SPACE

The Z380 CPU has the on-chip I/O address space to

control on-chip peripheral functions of the Superintegra-

tion

™

version of the devices. A portion of its interrupt

functions are also controlled by several on-chip registers,

which occupy an on-chip I/O address space. This on-chip

I/O address space can be accessed only with the following

reserved on-chip I/O instructions which are identical to the

Z180 original I/O instructions to access Page 0 I/O ad-

dressing area.

IN0

R,(n)

OTIM

IN0

(n)

OTIMR

OUT0

(n),R

OTDM

TSTIO n

OTDMR

When one of these I/O instructions is executed, the Z380

MPU outputs the register address being accessed in a

pseudo-transaction of two BUSCLK cycles duration, with

the address signals A31-A8 at zero. In the pseudo-trans-

actions, all bus control signals are at their inactive state.

The following four registers are assigned to this address-

ing space as a part of the Z380 CPU core:

Register Name

Internal I/O Address

Interrupt Enable Register

17H

Assigned Vector Base Register

18H

Trap and Break Register

19H

Chip Version ID Register

0FFH

The Chip Version ID register returns one byte data, which

indicates the version of the CPU, or the specific implemen-

tation of the Z380 CPU based Superintegration device.

Currently, the value 00H is assigned to the Z380 MPU, and

other values are reserved.

For the other three registers, refer to Chapter 6, “Interrupts

and Traps.”

Also, the Z380 MPU has registers to control chip selects,

refresh, waits, and I/O clock divide to Internal I/O address

00H to 10H. For these registers, refer to the Z380 MPU

Product specification (DC-3003-01).