3 select register, Iy bank select (iybank), Iy or iy’ register select (iy’) – Zilog Z80380 User Manual

Page 38: Ix bank select (ixbank), Ix or ix’ register select (ix’), Main bank select (mainbank), Bc/de/hl or bc’/de’/hl’ register select (alt), Extended mode (xm)

5-4

Z380

™

U

SER

'

S

M

ANUAL

DC-8297-03

Z

ILOG

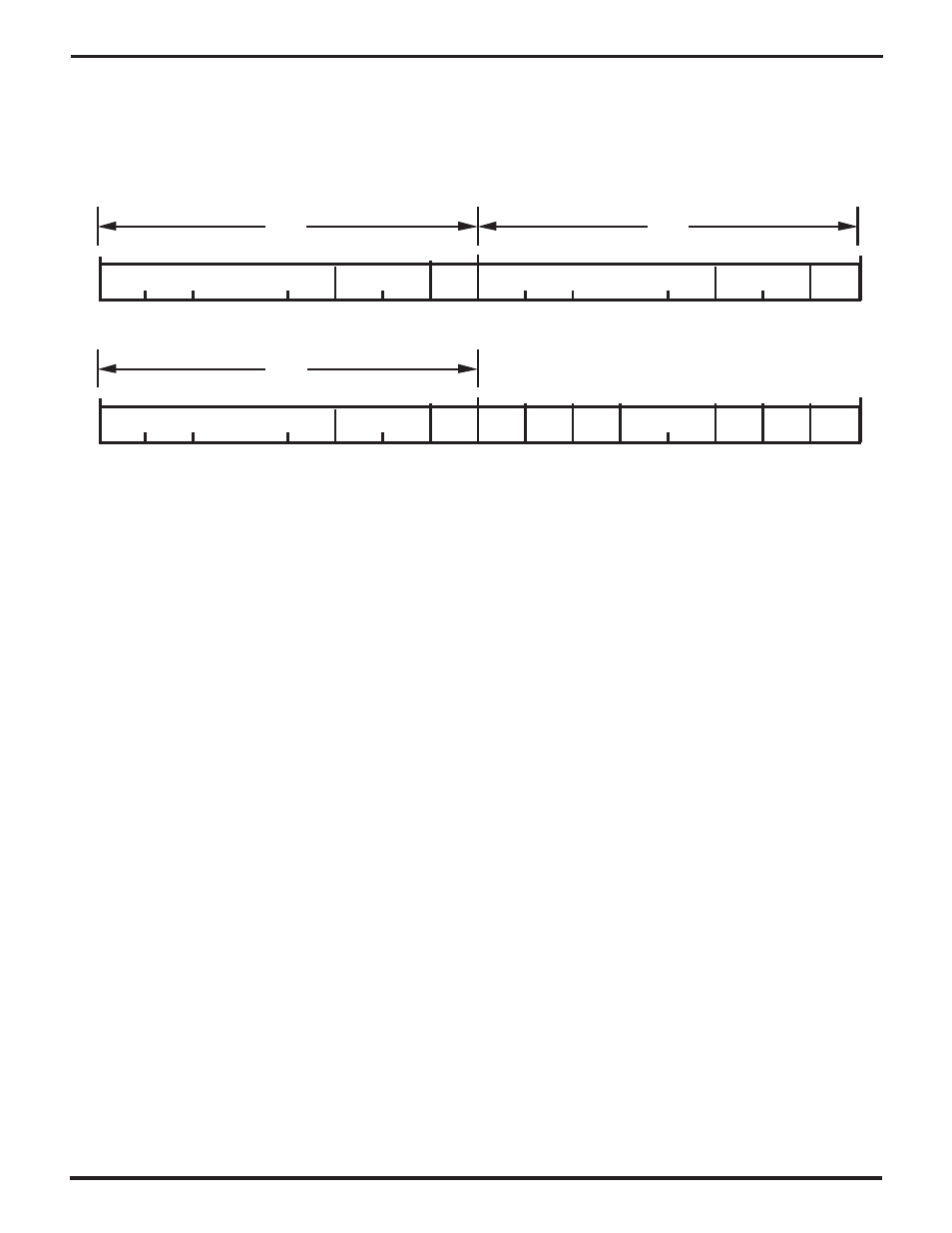

5.3 SELECT REGISTER

The Select Register (SR) controls the register set selection

and the operating modes of the Z380 CPU. The reserved

bits in the SR are for future expansion; they will always read

as zeros and should be written with zeros for future

compatibility. Access to this register is done by using the

newly added LDCTL instruction. Also, some of the instruc-

tions like EXX, IM p, and DI/EI change the bit(s). The SR

was shown in Figure 5-2.

Reserved (0)

23

21

22

17

IYBANK

IYP

Reserved (0)

IXBANK

IXP

20

18

19

16

31

29

30

25

28

26

27

24

XSR

YSR

Reserved (0)

7

5

6

1

MAINBANK

ALT

XM

IM

AFP

4

2

3

0

15

13

14

9

12

10

11

8

DSR

LW

IEF1

0

LCK

Figure 5-2. Select Register

5.3.1. IY Bank Select (IYBANK)

This 2-bit field selects the register set to be used for the IY

and IY’ registers. This field can be set independently of the

register set selection for the other Z380 CPU registers.

Reset selects Bank 0 for IY and IY’.

5.3.2. IY or IY’ Register Select (IY’)

This bit controls and reports whether IY or IY’ is the

currently active register. IY is selected when this bit is

cleared, and IY’ is selected when this bit is set. Reset

clears this bit, selecting IY.

5.3.3. IX Bank Select (IXBANK)

This 2-bit field selects the register set to be used for the IX

and IX’ registers. This field can be set independently of the

register set selection for the other Z380 CPU registers.

Reset selects Bank 0 for IX and IX’.

5.3.4. IX or IX’ Register Select (IX’)

This bit controls and reports whether IX or IX’ is the

currently active register. IX is selected when this bit is

cleared, and IX’ is selected when this bit is set. Reset

clears this bit, selecting IX.

5.3.5. Main Bank Select (MAINBANK)

This 2-bit field selects the register set to be used for the A,

F, BC, DE, HL, A’, F’, BC’, DE’, and HL’ registers. This field

can be set independently of the register set selection for

the other Z380 CPU registers. Reset selects Bank 0 for

these registers.

5.3.6. BC/DE/HL or BC’/DE’/HL’ Register

Select (ALT)

This bit controls and reports whether BC/DE/HL or BC’/DE’/

HL’ is the currently active bank of registers. BC/DE/HL is

selected when this bit is cleared, and BC’/DE’/HL’ is

selected when this bit is set. Reset clears this bit, selecting

BC/DE/HL.

5.3.7. Extended Mode (XM)

This bit controls the Extended/Native mode selection for

the Z380 CPU. This bit is set by the SETC XM instruction.

This bit can not be reset by software, only by Reset. When

this bit is set, the Z380 CPU is in Extended mode. Reset

clears this bit, and the Z380 CPU is in Native mode.