Stratix nios compact flash test – Altera High-Speed Development Kit, Stratix GX Edition User Manual

Page 125

Altera Corporation

Quartus II Version 3.0

7–43

Diagnostic Test Details

Nios Designs

Stratix Nios Compact Flash Test

The design is captured in a top-level BDF that controls the I/O pin names

and placements. Because this is a processor-based test, the actual test

consists of running several object files on the Nios processor and

observing the results in a terminal window on a PC.

The test uses the provided 32-MByte Kingston Technology compact flash

card. The test initializes the compact flash card and writes a sector of

random data to each usable sector and reads it back with a comparison.

f

Refer to “Compact Flash Interface (Stratix Nios Compact Flash)” on

page 5–32 for information on how to perform the test.

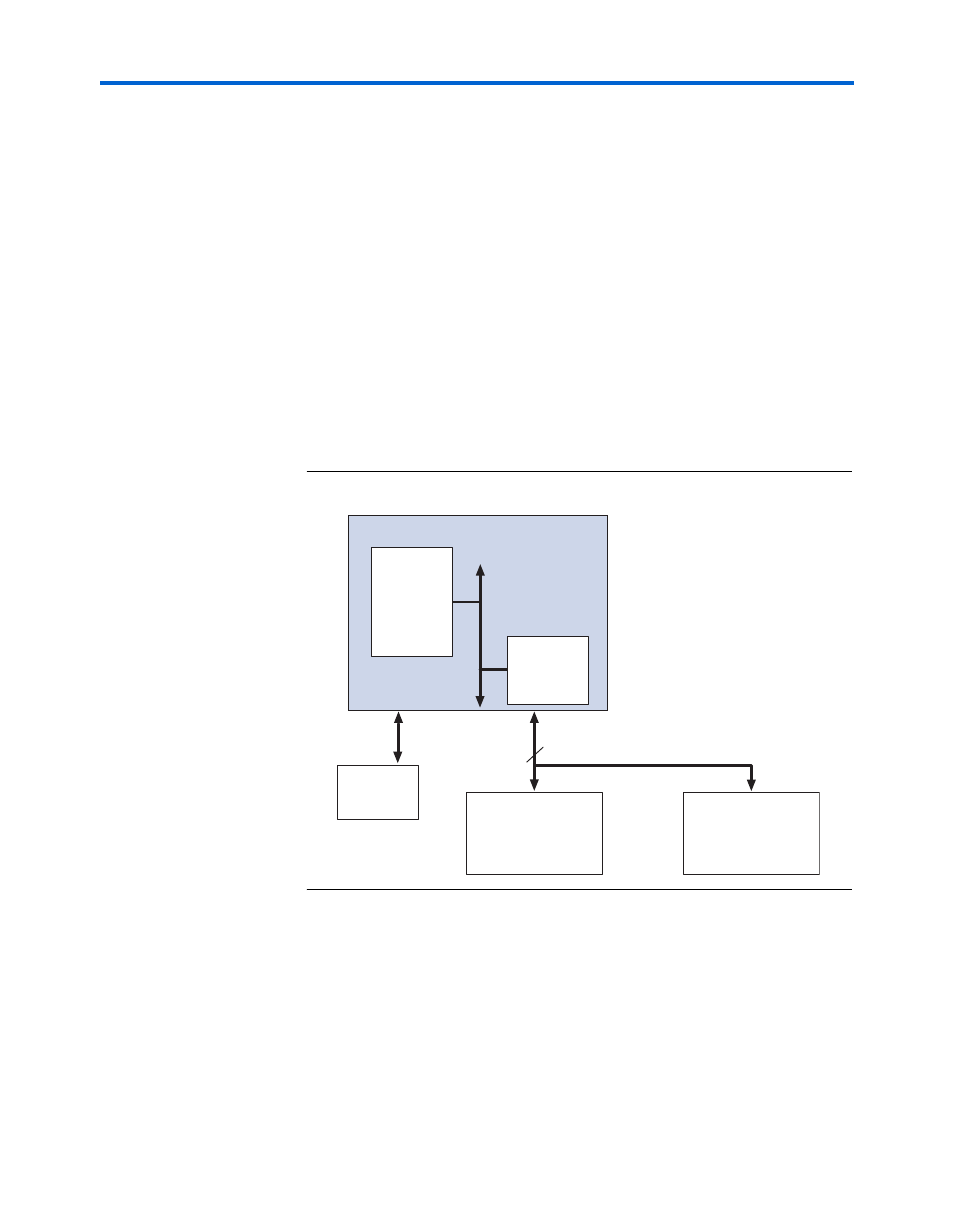

Figure 7–21 shows the Stratix Nios compact flash interface logic diagram

for the Stratix device.

Figure 7–21. Stratix Nios Compact Flash Interface Logic Diagram

In this design, the Nios processor controls an Avalon bus slave module

that interfaces to the compact flash card using the shared data bus of the

10/100 Ethernet network-interface card I/O connector interface. Because

these two interfaces share the same bus, you cannot use both interfaces at

the same time.

Stratix Device

32-MByte

Compact Flash

40

Status, Data & Control

RS-232

Port

Avalon

Bus

10/100 Ethernet

Network Interface Card

Nios

CPU

Avalon

Bus

Interface