Stratix gx hm-zd xcvr functional description – Altera High-Speed Development Kit, Stratix GX Edition User Manual

Page 106

7–24

Quartus II Version 3.0

Altera Corporation

Standard Tests

High-Speed Development Kit, Stratix GX Edition User Guide

(the first word of the PRBS sequence) data stream. When this pattern is

found, the data valid signal is asserted, which triggers an expected value

PRBS generator to start. The two data streams are sent to a comparator to

generate a match signal on a per channel basis. If the data streams match,

the match LED illuminates on a per channel basis. If the match signal goes

low while the data valid signal is high, the error flag is set and the error

counter is incremented. Pressing the reset button resets the system state,

error flag, and error count.

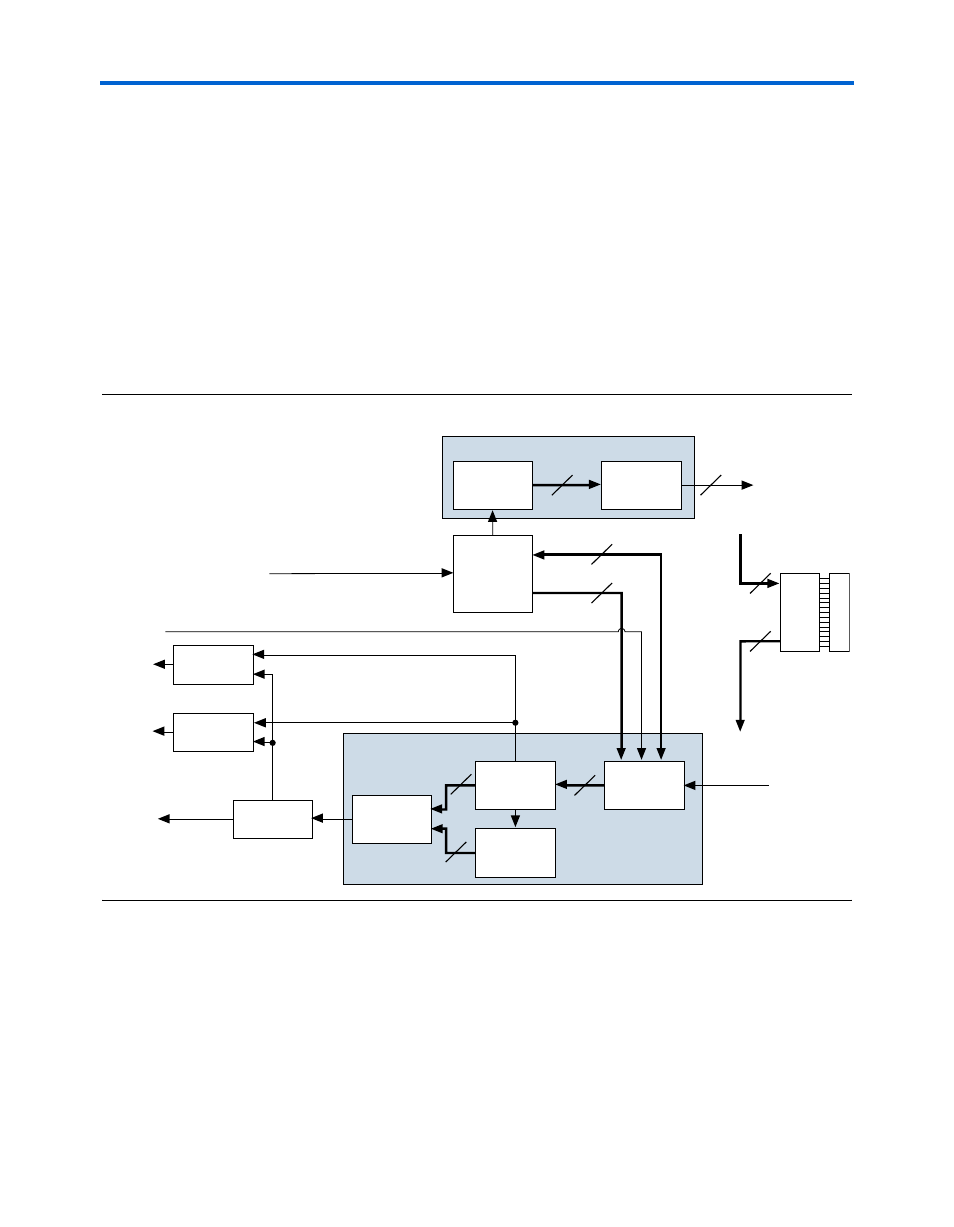

Stratix GX HM-Zd XCVR Functional Description

Figure 7–13 shows the Stratix GX HM-Zd XCVR logic diagram.

Figure 7–13. Stratix GX HM-Zd XCVR Test Logic Diagram

The GXB megafunction transmit PLL generates the system clock using

the 156.25-MHz crystal as the reference. The PLL generates a 156.25-MHz

clock to clock all of the data generation logic.

The transmit PRBS generator comprises 20 5-bit linear feedback shift

registers. The output is taken from the MSB of each shift register. The

initial seed value is 20’h695A7. When the enable (start) signal is high, the

generator outputs a 31-word sequence that repeats until stopped. On

PRBS

Generator

ALT GXB

TX

Transmit Channel (x4)

20

1

Start/Stop

Synchronization

Detect/Control

4

8

HM-Zd

Connector J1

HM-Zd XCVR

Loopback Card

4

4

Receive

Equalization

Dipswitch 1,0

ALTGXB

RX

Comparator

Receive Channel (x4)

20

20

22

Match

Register

Data Valid

Error

Register

Error

Counter

Data Valid

PRBS

Generator

7-Segment

Display

Error LED

Match LED

Pattern Detect/

Byte Swap