Altera High-Speed Development Kit, Stratix GX Edition User Manual

Page 122

7–40

Quartus II Version 3.0

Altera Corporation

Nios Designs

High-Speed Development Kit, Stratix GX Edition User Guide

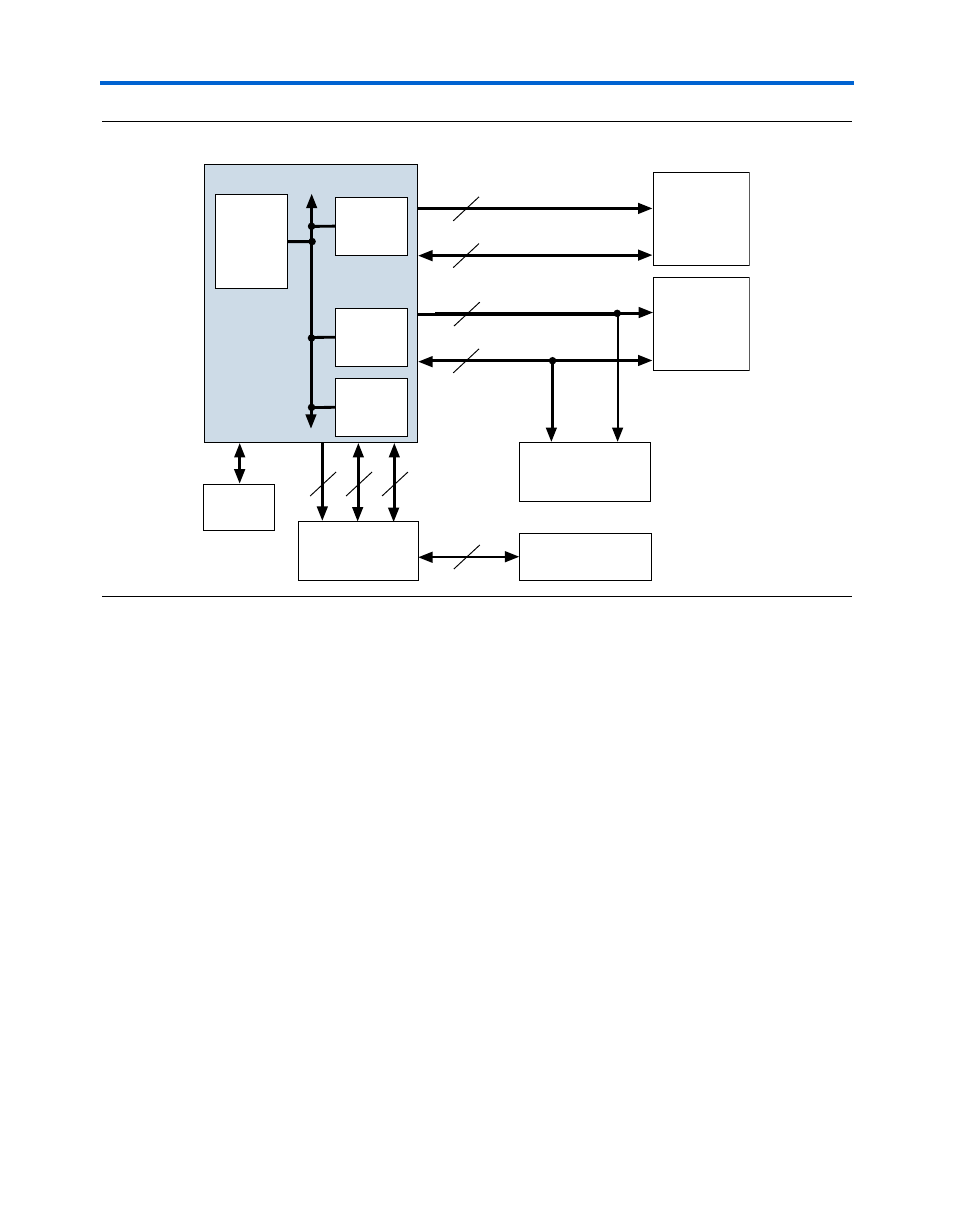

Figure 7–19. Stratix Nios Flash Memory & Ethernet Logic Diagram

The Nios processor controls three Avalon bus slave modules. The first

module handles all of the I/O signals and timing for the Stratix GX EPC16

configuration device. It controls the data, address, and controls signals

and reports status to the Nios processor. The second module controls

both the Stratix EPC16 device and the 4-Mbyte on-board flash chip. It is

configured with extra address signals for the on-board flash chip. The

third module interfaces with the LAN91C111 chip.

The test has two C programs: one to test the memories and one for the

LAN chip. The memory tests write the address of a location to that

location and read it back to confirm that the write operation was

successful. It repeats this operation for each memory device. If a

mismatch is found, it reports the error to the shell.

The Ethernet chip test runs the hello_plugs program. The test gives two

different results depending on whether the board is attached to a

network. If a board is not connected, the test initializes the chip and looks

for the network, but because the board is not connected, the test generates

timeouts. If a board is connected, the test uses DHCP to get a dynamic IP

address for the board.

On-Board

Flash

Stratix GX Address

Stratix GX Data

Stratix Address

Stratix Data

21

Add[20:0]

Data[15:0]

Add[20:0]

Data[15:0]

Add[21:0]

Data[16:0]

22

16

16

Stratix Device

Stratix GX

EPC16

Stratix

EPC16

MAC/PHY

(LAN91C111)

Integrated

RJ-45 Connector

A[14:0] D[31:0]

15

32

15

Status &

Control

4

RS-232

Port

Avalon

Bus

Inerface

Avalon

Bus

Interface

Avalon

Bus

Interface

Avalon

Bus

Nios

CPU