Application examples, Re f – Lenze EVS9332xS User Manual

Page 253

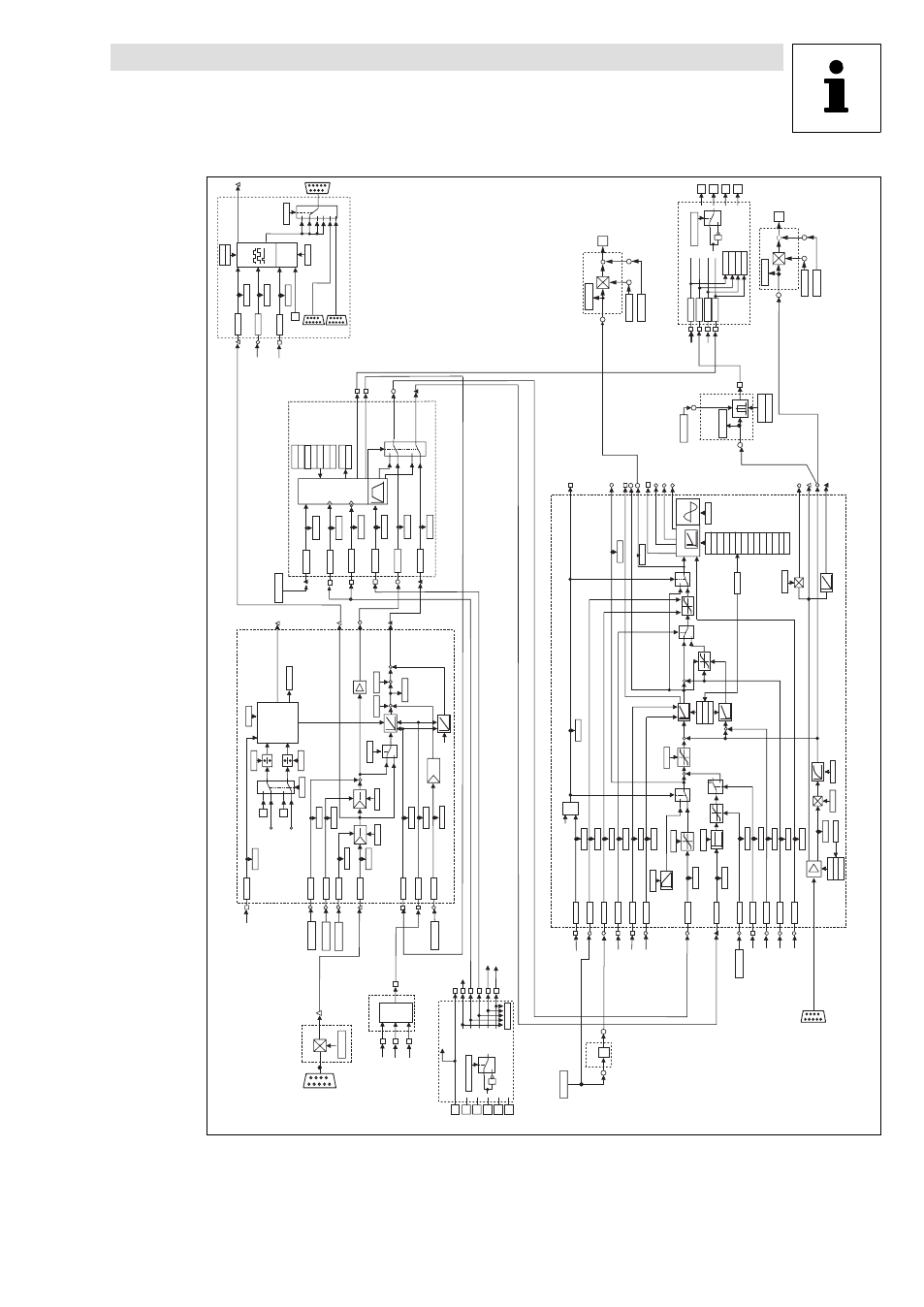

Application examples

4.6

Master frequency cascade − slave − drive (C0005 = 7000)

4−15

l

EDSVS9332S−EXT EN 2.0

Act.

phase

Phase

trimming

Phase

trimming=f(n)

i

Set

phase

Phase

offset

S

peed

trimming

C

00

30

C

05

40

C

TR

L

D

FO

U

T-

A

N

-IN

C

05

47

C

05

41

D

FO

U

T-

D

F-

IN

C

05

49

C

05

42

C

05

48

C

05

44

D

FO

U

T-

S

Y

N

-R

D

Y

D

FO

U

T-

O

U

T

D

F

O

U

T

C

05

45

1

0

2

3

4

5

X

8

X

9

X

1

0

C

05

40

E

5

X

5

C

04

74

/1

FI

X

E

D

0

FI

X

E

D

0%

FI

X

E

D

0

FI

X

E

D

10

0%

FI

X

E

D

0%

FI

X

E

D

0

D

IG

IN

1

S

peed

limit

ation

S

peed

controller

T

orque

limit

ation

Actual

speed

Phase

controller

Current

controller

C

04

25

D

F

IN

C

04

72

/5

C

00

32

C

04

73

/1

C

04

73

/3

C

IN

H

O

R

1

1

Q

S

P

C

00

17

C

06

80

C

06

81

C

06

83

/1

C

M

P

1

A

N

E

G

C

04

72

/3

*-

1

FI

X

E

D

0

FI

XE

D

1

FI

X

E

D

0%

FI

X

E

D

0%

C

04

72

/6

Q

S

P

TR

IP

-S

E

T

TR

IP

-R

E

S

E

T

FI

X

E

D

0

N

A

C

T=

0

TR

IP

R

D

Y

N

A

C

T=

0

N

A

C

T=

0

X

9

*

a b b

a

*

a b b

a

+

+

1

0

+

+

C

05

37

C

05

36

/2

C

05

36

/1

C

00

33

C

05

33

C

05

30

C

02

52

C

05

36

/3

C

05

38

/2

C

05

39

D

F

S

E

T

D

F

S

E

T

-N

O

U

T

+

-

D

F

S

E

T

-A

-T

R

IM

D

F

S

E

T

-N

-T

R

IM

D

F

S

E

T

-R

A

T

-D

IV

D

F

S

E

T

-R

E

S

E

T

D

F

S

E

T

-I

N

D

F

S

E

T

-P

S

E

T

D

F

S

E

T

-V

P

-D

IV

D

F

S

E

T

-P

O

U

T

D

F

S

E

T

-S

E

T

C

05

38

/3

+

+

C

02

53

C

05

31

C

05

35

C

05

32

2

1

2

1

E

4

E

5

X

5

X

5

X

9

/6

,7

M

C

T

R

L

-P

H

I-

A

C

T

C

05

38

/1

D

F

S

E

T

-0

-P

U

L

S

E

D

F

S

E

T

-A

C

K

C

05

25

C

05

22

C

05

24

C

05

21

C

05

20

C

05

27

C

05

26

C

05

23

C

05

34

*

C

05

29

C

05

28

/1

C

05

28

/2

C

TR

L

E

1

E

2

E

3

E

4

E

5

1

0

C

01

14

/1

...

5

D

IG

IN

D

IG

IN

1

D

IG

IN

2

D

IG

IN

3

D

IG

IN

4

D

IG

IN

5

C

04

43

2

8

D

C

T

R

L

-X

5/

28

X

5

D

IG

IN

-C

IN

H

1

R

E

F

R

E

F

-N

-I

N

R

E

F

-P

H

I-

IN

R

E

F

-N

-S

E

T

R

E

F

-P

S

E

T

R

E

F

-O

N

R

E

F

-B

U

S

Y

R

E

F

-O

K

R

E

F

-M

A

R

K

C

09

29

C

09

23

C

09

28

C

09

22

C

09

27

/2

C

09

21

C

09

27

/1

C

09

20

C

T

R

L

C

09

35

C

09

36

C

09

31

C

09

32

C

09

30

C

09

34

C

09

33

R

E

F

-P

O

S

-L

O

A

D

R

E

F

-A

C

T

P

O

S

-I

N

C

09

26

/1

C

09

25

C

09

27

/3

C

09

24

C

09

26

/3

C

09

26

/4

1

0

C

01

05

C

02

54

+

-

C

09

08

C

00

70

C

00

71

+

-

1

+

1

0

C

00

22

C

00

81

C

00

87

C

00

88

C

00

89

C

00

90

C

00

91

P

W

M

C

04

20

C

04

90

C

04

95

M

C

TR

L-

P

H

I-S

E

T

M

C

TR

L-

N

2-

LI

M

M

C

TR

L-

M

-A

D

D

M

C

T

R

L-

P

H

I-

LI

M

M

C

TR

L-

P

H

I-O

N

C

09

06

/2

M

C

TR

L-

N

-S

E

T

V

E

C

T

-C

T

R

L

M

C

TR

L-

N

S

E

T2

M

C

T

R

L

M

C

TR

L-

N

A

C

T

M

C

TR

L-

P

H

I-A

C

T

C

09

06

/6

C

09

06

/1

M

C

T

R

L-

N

/M

-S

W

T

1

0

M

C

TR

L-

H

I-M

-L

IM

M

C

TR

L-

LO

-M

-L

IM

C

00

51

+

+

C

00

50

C

00

18

C

00

06

C

00

84

C

00

85

C

00

86

C

00

25

M

C

TR

L-

M

M

A

X

C

09

09

C

00

11

10

0%

C

00

72

C

09

06

/5

C

09

07

/1

M

C

TR

L-

FL

D

-W

E

A

K

C

09

06

/7

M

C

TR

L-

I-S

E

T

C

09

06

/8

M

C

TR

L-

I-L

O

A

D

C

09

07

/4

M

C

TR

L-

Q

S

P

C

09

07

/3

C

09

07

/2

C

09

06

/3

C

09

06

/4

C

08

93

C

08

92

C

08

99

C

09

00

C

09

02

C

09

01

C

08

90

C

08

94

C

08

95

C

08

97

C

08

96

C

08

91

C

08

98

M

C

TR

L-

Q

S

P

-O

U

T

R

E

S

O

LV

E

R

D

C

TR

L-

Q

S

P

1

M

C

TR

L-

M

A

C

T

M

C

TR

L-

D

C

V

O

LT

C

00

42

M

C

TR

L-

P

H

I-A

N

A

C

O

N

S

T

+

+

C

04

97

X

7

M

C

TR

L-

P

H

I-A

N

G

C

00

75

C

00

76

C

00

77

C

00

78

Q

S

P

decel.

ramp

A

1

A

2

A

3

A

4

1

0

C

01

18

/1

...

4

D

IG

O

U

T

D

IG

O

U

T1

D

IG

O

U

T2

D

IG

O

U

T3

D

IG

O

U

T4

C

01

17

/1

C

01

17

/2

C

01

17

/3

C

01

17

/4

C

04

44

/4

C

04

44

/3

C

04

44

/2

C

04

44

/1

X

5

1

6

3

C

01

08

/2

C

01

09

/2

C

43

9/

1

+

+

X

6

AOUT

2

6

2

C

01

08

/1

C

01

09

/1

C

43

4/

1

+

+

X

6

AOUT1

M

M

C

C

T

T

R

R

L

L -

- M

M

S

S

E

E

T

T 2

1

M

C

TR

L-

IM

A

X

C

00

56

M

C

TR

L

IA

C

T

9300STD326

Fig. 4−7

Signal flow diagram for configuration 7000