22 receiver status (16h), Cs8422 – Cirrus Logic CS8422 User Manual

Page 62

62

DS692F2

CS8422

96KHZ – Indicates the frequency range of the sample rate of incoming AES3 data (Fsi). If Fsi

49 kHz or

Fsi

120 kHz, this bit will output a “0”. If 60 kHz Fsi 98 kHz, this bit will output a “1”. Otherwise the output

is indeterminate.

192KHZ – Indicates the frequency range of the sample rate of incoming AES3 data (Fsi). If Fsi

98 kHz,

this bit will output a “0”. If Fsi

120 kHz, this bit will output a “1”. Otherwise the output is indeterminate.

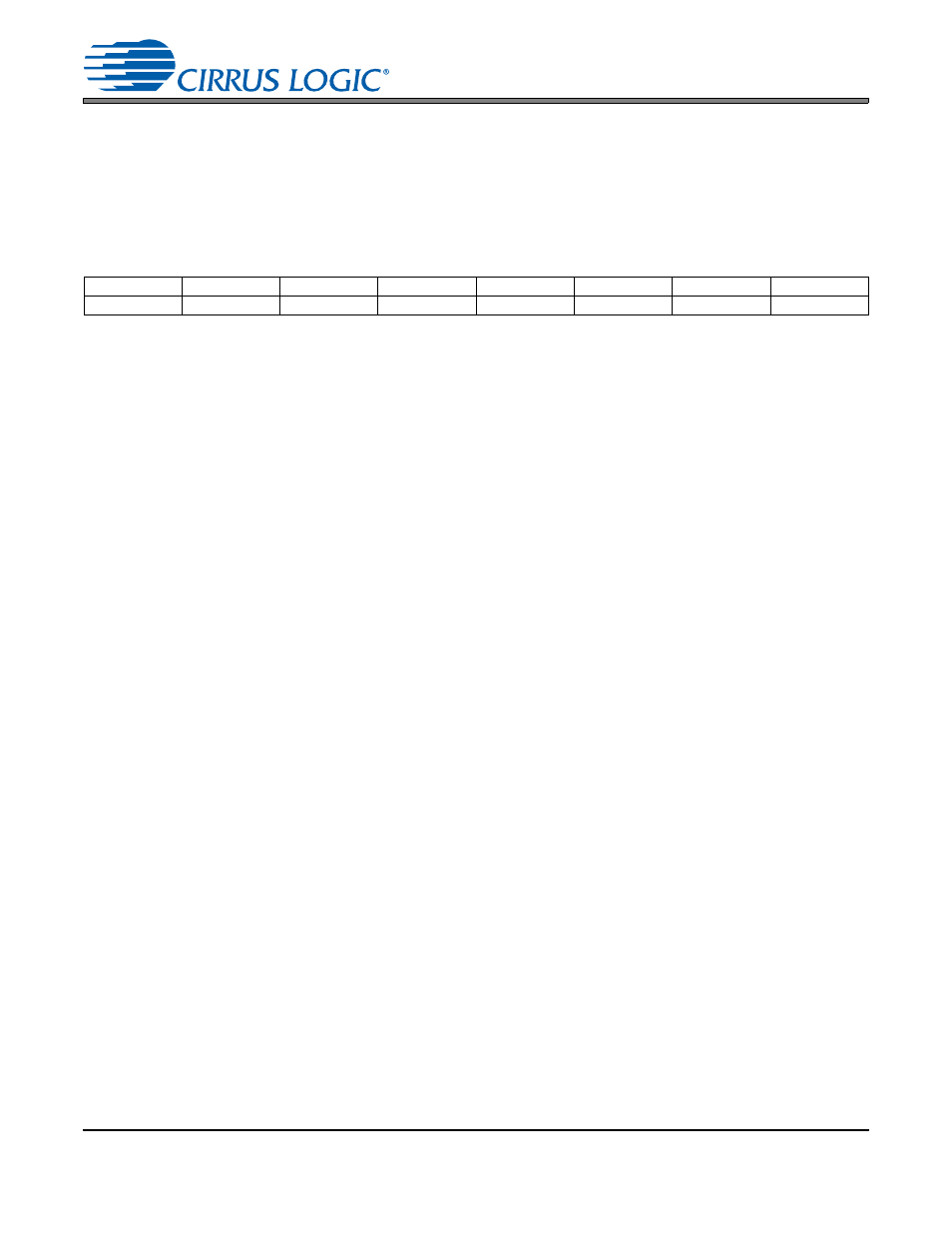

11.22 Receiver Status (16h)

CS_UPDATE - Determines whether channel status registers and RCVR_RATE are updated in the presence

of

a receiver error (register 14h).

0 - The receiver channel status registers and RCVR_RATE are updated on each AES3 block boundary.

1 - The receiver channel status registers and RCVR_RATE are updated on each AES3 block boundary if

no biphase, confidence, parity, or CRCC error has occurred during the reception of the channel status

block.

RCVR_RATE - Input sample rate represented in the channel status data of incoming AES3 data.

00 - Reserved

01 - 32 kHz

10 - 44.1 kHz

11 - 48 kHz

RX_LOCK - AES3 Receiver PLL Lock

0 - The PLL has not achieved lock for more than 2 Z preambles or AES3 input is not driving PLL.

1 - Goes high 2 Z preambles after the PLL has achieved lock when an AES3 input has been selected to

drive the PLL.

BLK_VERR - Block Validity Error. Updated on DETC boundaries

0 - The Validity bit of the incoming AES3 data has remained low during the input of the last AES3 data

block.

1 - The Validity bit of incoming AES3 data has gone high at some point during the input of the last AES3

data block.

BLK_CERR - Block Confidence Error. Updated on DETC boundaries

0 - The Confidence bit associated with incoming AES3 data has remained high during the input of the last

AES3 data block.

1 - The Confidence bit associated with incoming AES3 data has gone low at least once during the input

of the last AES3 data block.

BLK_BERR - Block Biphase Error. Updated on DETC boundaries

0 - There has been no biphase error associated with incoming AES3 data during the input of the last AES3

data block.

7

6

5

4

3

2

1

0

CS_UPDATE RCVR_RATE1 RCVR_RATE0

RX_LOCK

BLK_VERR

BLK_CERR

BLK_BERR

BLK_PERR

0

-

-

-

-

-

-

-