Note 7), Note 8), Cs8422 – Cirrus Logic CS8422 User Manual

Page 18

18

DS692F2

CS8422

Notes:

7.

After powering up the CS8422, RST should be held low until the power supplies and clocks are settled.

8.

If ISCLK is selected as the clock source for the PLL, then the Sample Rate = ISCLK/64.

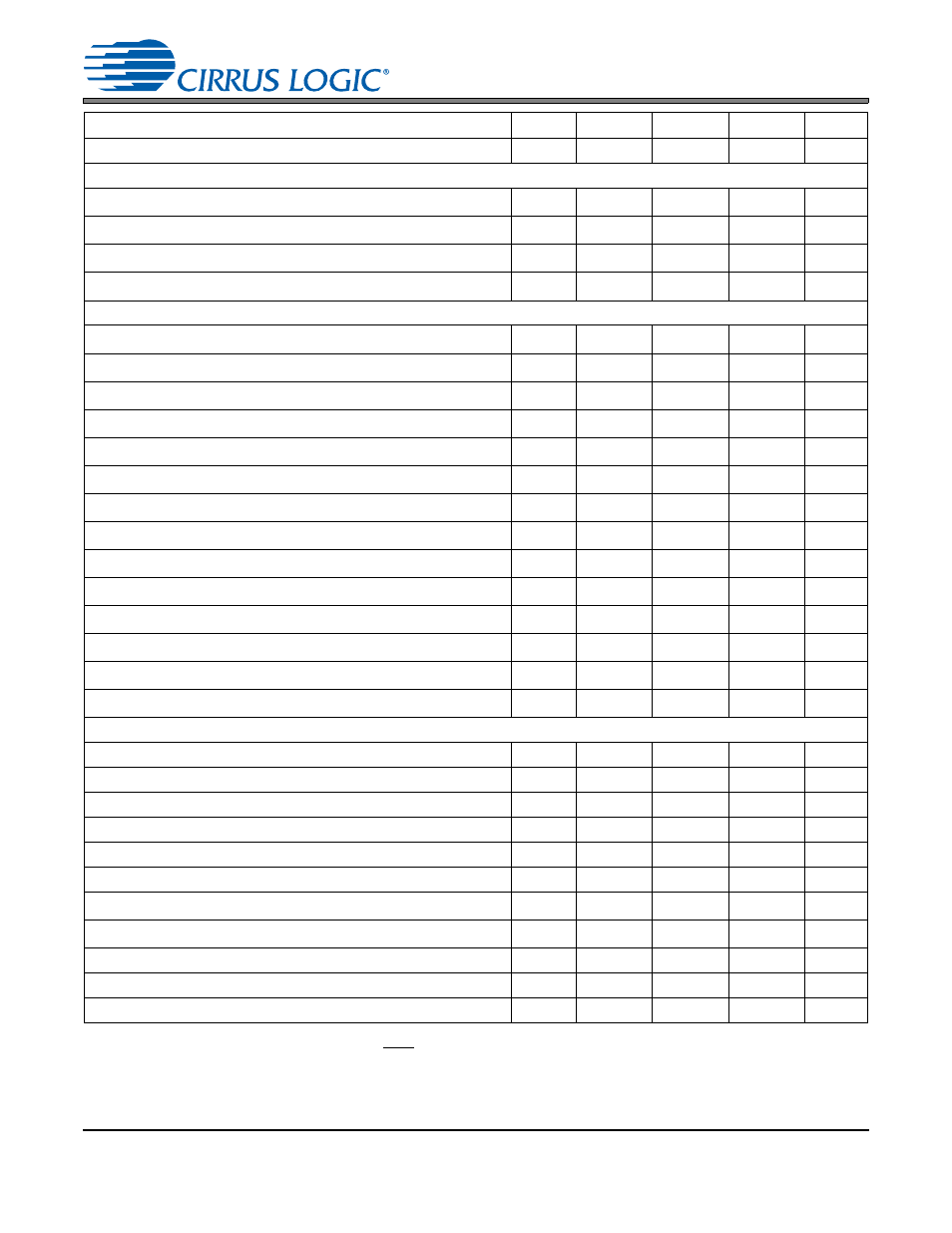

TDM Mode OSCLK Falling Edge to OLRCK Edge

t

fsm

-

-

4.2

ns

VL = 1.8 V, 2.5 V

RMCK/MCLK_OUT Output Frequency (VL = 1.8 V)

-

-

13.5

MHz

RMCK/MCLK_OUT Output Frequency (VL = 2.5 V)

-

-

31

MHz

RMCK/MCLK_OUT Output Duty Cycle (VL = 1.8 V)

37

50

63

%

RMCK/MCLK_OUT Output Duty Cycle (VL = 2.5 V)

45

50

55

%

Slave Mode

ISCLK Frequency

-

-

49.152

MHz

ISCLK High Time

t

sckh

9.2

-

-

ns

ISCLK Low Time

t

sckl

9.2

-

-

ns

OSCLK Frequency

-

-

15.7

MHz

OSCLK High Time

t

sckh

28.7

-

-

ns

OSCLK Low Time

t

sckl

28.7

-

-

ns

I/OLRCK Edge to I/OSCLK Rising Edge

t

lcks

7.4

-

-

ns

I/OSCLK Rising Edge to I/OLRCK Edge

t

lckd

6.2

-

-

ns

OSCLK Falling Edge/OLRCK Edge to SDOUT Output Valid

t

dpd

-

-

29.5

ns

SDIN/TDM_IN Setup Time Before I/OSCLK Rising Edge

t

ds

4.7

-

-

ns

SDIN/TDM_IN Hold Time After I/OSCLK Rising Edge

t

dh

7.3

-

-

ns

TDM Mode OLRCK High Time

t

lrckh

20

-

-

ns

TDM Mode OLRCK Rising Edge to OSCLK Rising Edge

t

fss

7.0

-

-

ns

TDM Mode OSCLK Rising Edge to OLRCK Falling Edge

t

fsh

6.2

-

-

ns

Master Mode

I/OSCLK Frequency (non-TDM Mode)

48*Fsi/o

-

128*Fsi/o

MHz

I/OLRCK Duty Cycle

45

-

55

%

I/OSCLK Duty Cycle

45

-

55

%

I/OSCLK Falling Edge to I/OLRCK Edge

t

lcks

-

-

5.7

ns

OSCLK Falling Edge to SDOUT Output Valid (VL = 1.8 V)

t

dpd

-

-

11.2

ns

OSCLK Falling Edge to SDOUT Output Valid (VL = 2.5 V)

t

dpd

-

-

6.4

ns

SDIN Setup Time Before I/OSCLK Rising Edge

t

ds

4.7

-

-

ns

SDIN Hold Time After I/OSCLK Rising Edge

t

dh

7.3

-

-

ns

TDM Mode OSCLK Frequency

-

-

31

MHz

TDM Mode OSCLK Falling Edge to OLRCK Edge (VL = 1.8V)

t

fsm

-

-

9.6

ns

TDM Mode OSCLK Falling Edge to OLRCK Edge (VL = 2.5V)

t

fsm

-

-

5.7

ns

Parameter

Symbol Min

Typ

Max

Units