Cirrus Logic CS8422 User Manual

Cs8422, Sample rate converter features, Digital audio interface receiver features

Copyright

Cirrus Logic, Inc. 2012

(All Rights Reserved)

24-bit, 192-kHz, Asynchronous Sample Rate Converter with

Integrated Digital Audio Interface Receiver

Sample Rate Converter Features

140 dB Dynamic Range

-120 dB THD+N

No External Master Clock Required

Supports Sample Rates up to 211 kHz

Input/Output Sample Rate Ratios from 6:1 to

1:6

Master Mode Master Clock/Sample Rate Ratio

Support: 64, 96, 128, 192, 256, 384, 512, 768,

1024

16, 18, 20, or 24-bit Data I/O

Dither Automatically Applied and Scaled to

Output Resolution

Multiple Device Outputs are Phase Matched

Digital Audio Interface Receiver

Features

Complete EIAJ CP1201, IEC-60958, AES3,

S/PDIF Compatible Receiver

28 kHz to 216 kHz Sample Rate Range

2:1 Differential AES3 or 4:1 S/PDIF Input Mux

De-emphasis Filtering for 32 kHz, 44.1 kHz,

and 48 kHz

Recovered Master Clock Output: 64 x Fs,

96 x Fs, 128 x Fs, 192 x Fs, 256 x Fs,

384 x Fs, 512 x Fs, 768 x Fs, 1024 x Fs

49.152 MHz Maximum Recovered Master

Clock Frequency

Ultralow-jitter Clock Recovery

High Input Jitter Tolerance

No External PLL Filter Components Required

Selectable and Automatic Clock Switching

AES3 Direct Output and AES3 TX Pass-

through

On-chip Channel Status Data Buffering

Automatic Detection of Compressed Audio

Streams

Decodes CD Q Sub-Code

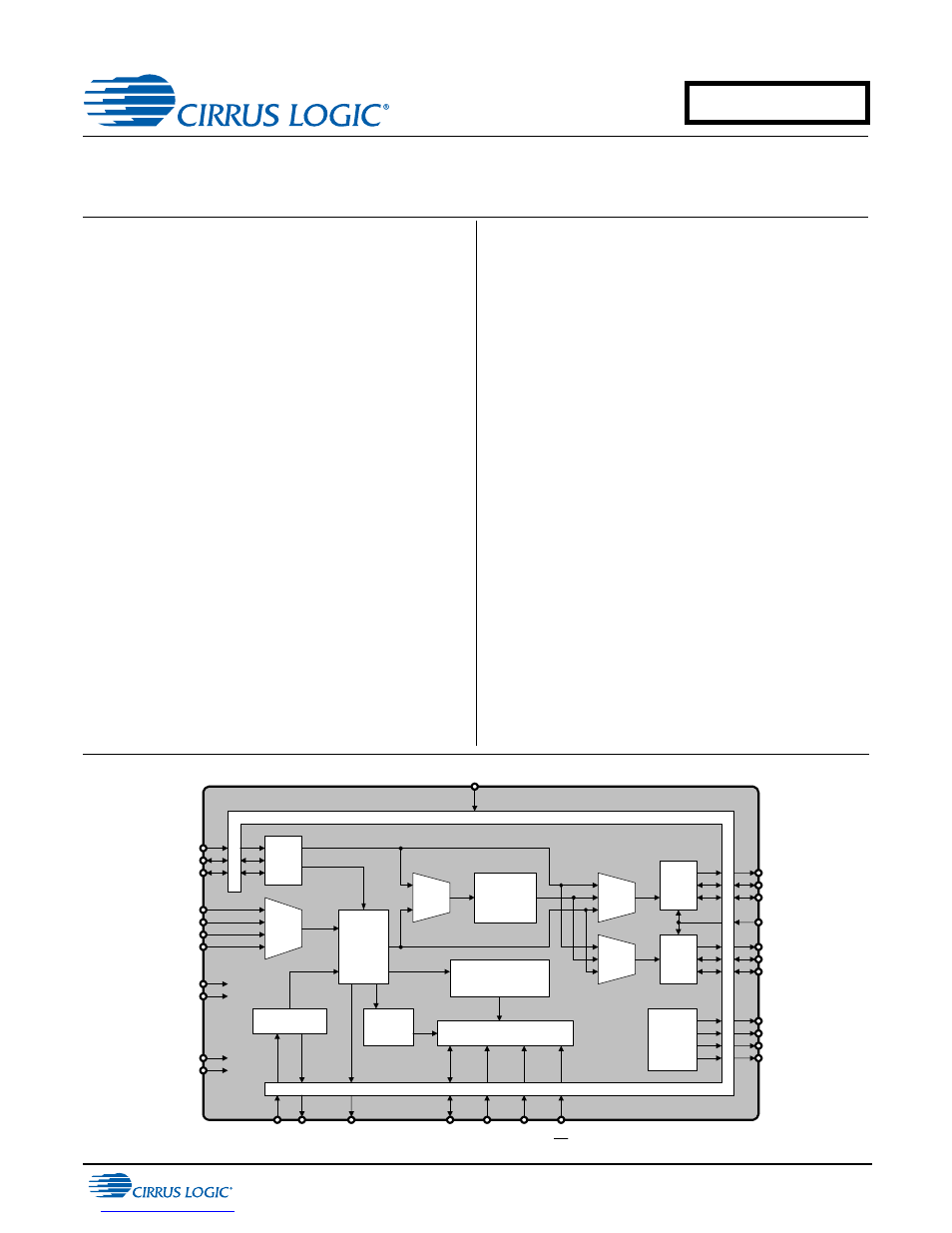

Serial

Audio

Input

4:1

MUX

RX0/RXP0

RX1/RXN0

RX2/RXP1

RX3/RXN1

Receiver

Clock &

Data

Recovery

(PLL)

ILRCK

ISCLK

SDIN

Sample

Rate

Converter

C or U Data Buffer

(First 5 Bytes)

Control Port & Registers

2:1

MUX

Serial

Audio

Output

3:1

MUX

XTI

Clock

Generator

SDA/

CDOUT

SCL/

CCLK

AD1/

CDIN

AD0/

CS

RMCK

General

Purpose

Outputs

GPO0

Format

Detect

GPO1

GPO2

GPO3

OLRCK1

OSCLK1

SDOUT1

TDM_IN

Serial

Audio

Output

3:1

MUX

OLRCK2

OSCLK2

SDOUT2

VL

VA

AGND

XTO

Level Translators

Level Translators

DGND

V_REG

NOV '12

DS692F2

CS8422

Document Outline

- Table of Contents

- List of Figures

- List of Tables

- 1. Pin Description

- 2. Characteristics and Specifications

- 3. Typical Connection Diagrams

- 4. Overview

- 5. Three-Wire Serial Input/Output Audio Port

- 6. Digital Interface Receiver

- 6.1 AES3 and S/PDIF Standards

- 6.2 Receiver Input Multiplexer

- 6.3 Recovered Master Clock - RMCK

- 6.4 XTI System Clock Mode

- 6.5 AES11 Behavior

- 6.6 Error and Status Reporting

- 6.7 Non-Audio Detection

- 6.8 Format Detection (Software Mode Only)

- 6.9 Interrupts (Software Mode Only)

- 6.10 Channel Status and User Data Handling

- 7. Sample Rate Converter (SRC)

- 8. Hardware Mode Control

- 9. Software Mode Control

- 10. Register Quick Reference

- 11. Software Register Bit Definitions

- 11.1 CS8422 I.D. and Version Register (01h)

- 11.2 Clock Control (02h)

- 11.3 Receiver Input Control (03h)

- 11.4 Receiver Data Control (04h)

- 11.5 GPO Control 1 (05h)

- 11.6 GPO Control 2 (06h)

- 11.7 Serial Audio Input Clock Control (07h)

- 11.8 SRC Output Serial Port Clock Control (08h)

- 11.9 Recovered Master Clock Ratio Control & Misc. (09h)

- 11.10 Data Routing Control(0Ah)

- 11.11 Serial Audio Input Data Format (0Bh)

- 11.12 Serial Audio Output Data Format - SDOUT1 (0Ch)

- 11.13 Serial Audio Output Data Format - SDOUT2 (0Dh)

- 11.14 Receiver Error Unmasking (0Eh)

- 11.15 Interrupt Unmasking (0Fh)

- 11.16 Interrupt Mode (10h)

- 11.17 Receiver Channel Status (11h)

- 11.18 Format Detect Status (12h)

- 11.19 Receiver Error (13h)

- 11.20 Interrupt Status (14h)

- 11.21 PLL Status (15h)

- 11.22 Receiver Status (16h)

- 11.23 Fs/XTI Ratio (17h - 18h)

- 11.24 Q-Channel Subcode (19h - 22h)

- 11.25 Channel Status Registers (23h - 2Ch)

- 11.26 IEC61937 PC/PD Burst preamble (2Dh - 30h)

- 12. Applications

- 13. Performance Plots

- 14. Package Dimensions

- 15. Thermal Characteristics and Specifications

- 16. Ordering Information

- 17. References

- 18. Revision History