3 src muting, 4 src master clock, 3 src muting 7.4 src master clock – Cirrus Logic CS8422 User Manual

Page 38: Table 2. pll clock ratios, Src master, K. see, Ster clock. see, Src master clock, Cs8422

38

DS692F2

CS8422

7.3

SRC Muting

The SDOUT pin sourced by the SRC (SDOUT1 or SDOUT2 in Software Mode, SDOUT1 in Hardware

Mode) is set to all zero output (full mute) immediately after the RST pin is set high. While the output from

the SRC becomes valid, SDOUT will be soft unmuted over a period of approximately 27488/Fsi while in in-

terpolation mode (Fsi < Fso) or 54976/Fso while in decimation mode (Fsi > Fso). When the output becomes

invalid the SRC’s SDOUT is immediately set to all zero output (hard muted). After all invalid states have

been cleared, the SRC will soft unmute SDOUT.

7.4

SRC Master Clock

The CS8422 can use the clock signal supplied through XTI-XTO, the PLL, or an internal ring oscillator as

its master clock (MCLK). If the SRC MCLK source is selected as being XTI-XTO, care must be taken to en-

sure that the SRC MCLK source does not exceed 33 MHz. If the SRC MCLK source exceeds 33 MHz, an

internal clock divider can be enabled to divide the SRC MCLK source by 2, allowing the use of higher fre-

quency clocks. See

and

If the SRC MCLK is applied through XTI then it can be supplied from a digital clock source, a crystal oscil-

lator, or a fundamental mode crystal. If XTO is not used, such as with a digital clock source or crystal oscil-

lator, XTO should be left unconnected or pulled low through a 20 k

resistor to GND.

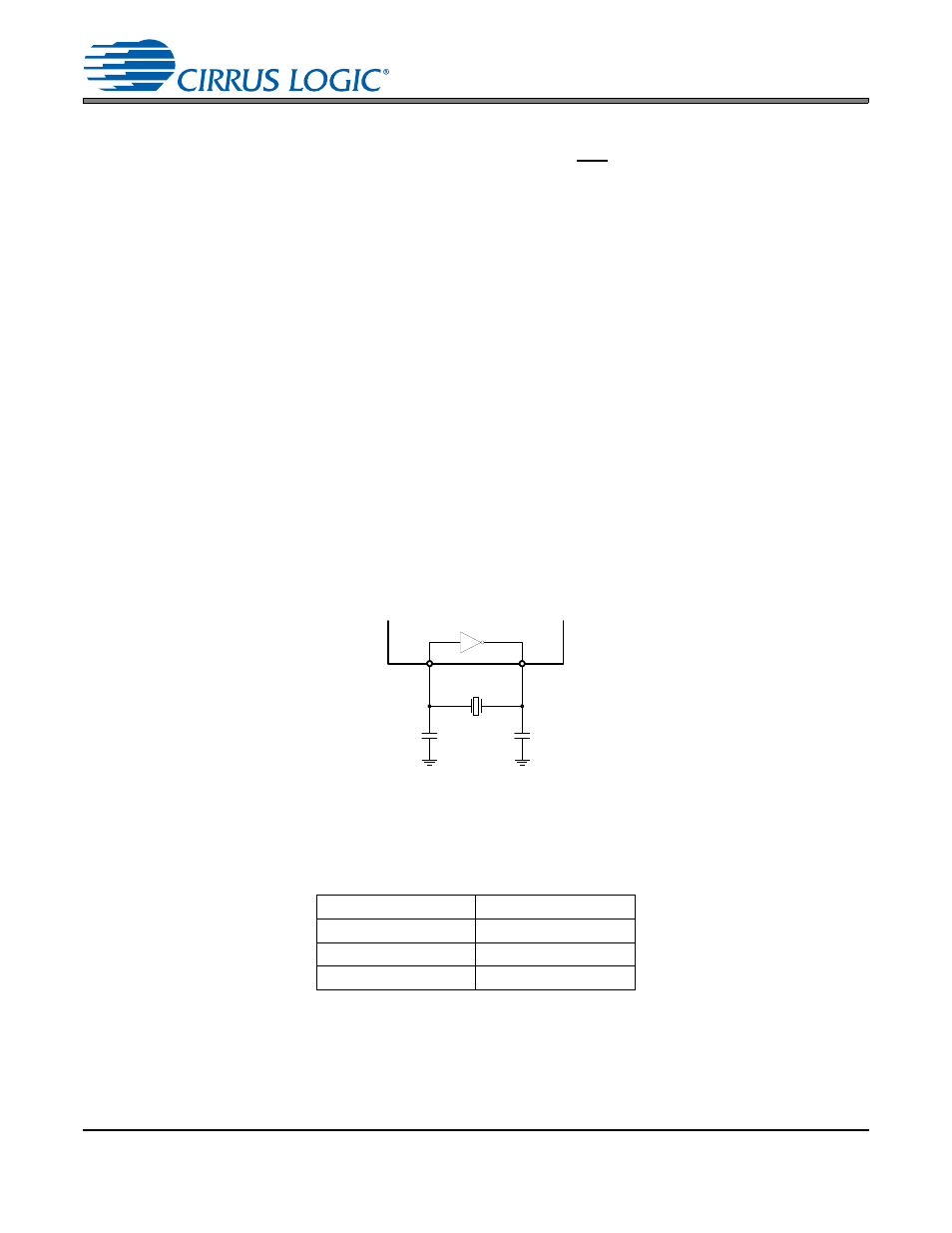

If a crystal in conjunction with the internal oscillator is used to supply the SRC MCLK, the crystal circuit

should be connected as shown in

. If VL < 2.5 Volts, it is recommended that the crystal attached

across XTI and XTO should be specified as operating with a load capacitance of 10pF (capacitors in

should be 20 pF). If VL

2.5 Volts, it is recommended that the crystal attached across XTI and

XTO should be specified as operating with a series capacitance of at 20pF (capacitors in

should

be at 40 pF). Please refer to the crystal manufacturer’s specifications for more information about external

capacitor recommendations.

If the PLL clock is selected as the SRC MCLK, the SRC MCLK will be synchronous to incoming AES3-com-

patible data or ISCLK. Unlike RMCK, the user does not control PLL clock’s relationship to the sampling rate

of incoming AES3-compatible data (Fsi), or ISCLK. See

for the relationship between the Fsi or IS-

CLK/64, and the PLL clock.

The CS8422 has the ability to operate without a master clock input through XTI. This benefits the design by

not requiring extra external clock components (lowering production cost) and not requiring a master clock

to be routed to the CS8422, resulting in lowered noise contribution in the system. In this mode, an internal

Fsi (or ISCLK/64)

PLL/Fsi

Fsi

49 kHz

512

60 kHz

Fsi 98 kHz 256

120 kHz

Fsi

128

Table 2. PLL Clock Ratios

XTI

XTO

C

C

Figure 20. Typical Connection Diagram for Crystal Circuit