Switching specifications, Cs8422 switching specifications – Cirrus Logic CS8422 User Manual

Page 17

DS692F2

17

CS8422

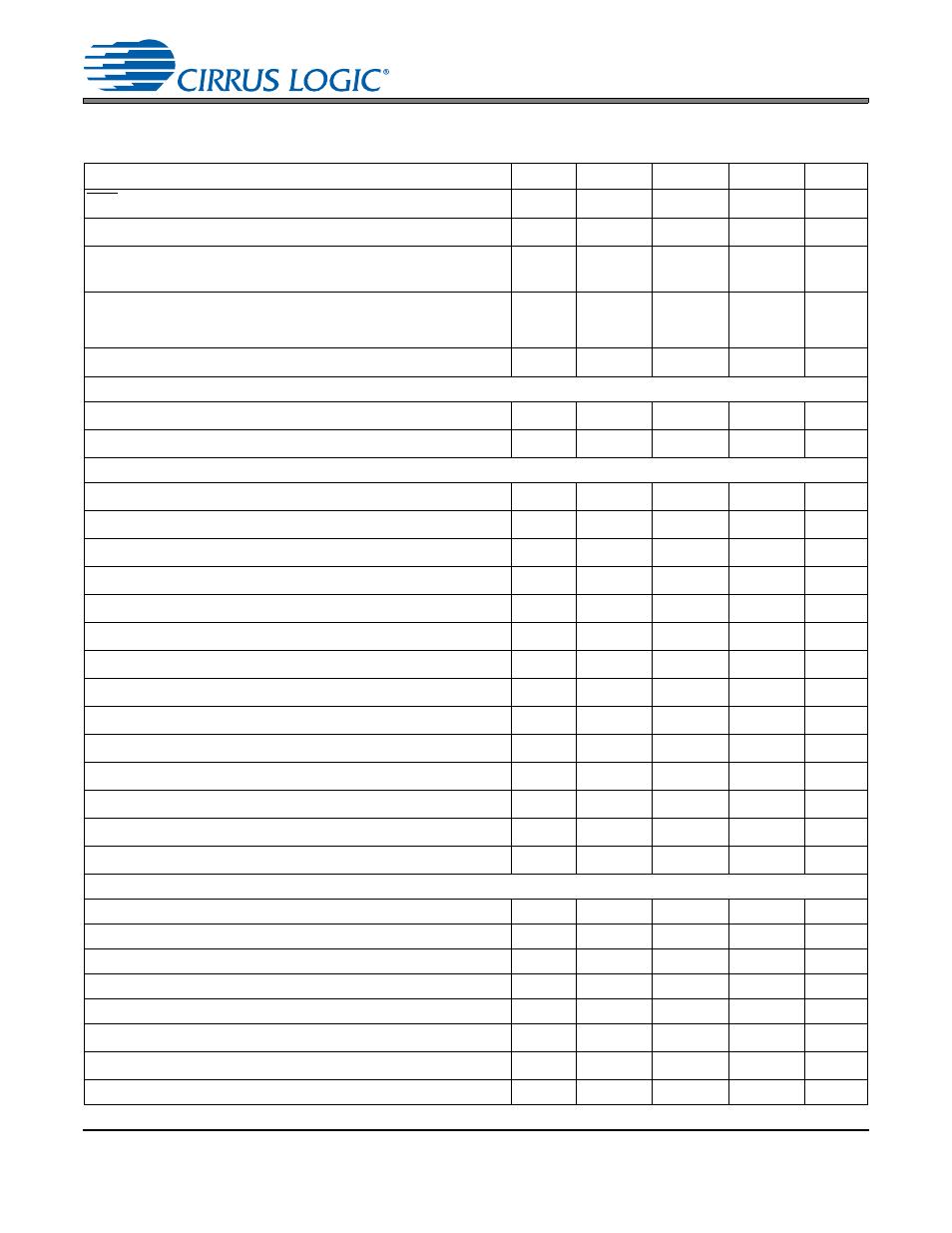

SWITCHING SPECIFICATIONS

Inputs: Logic 0 = 0 V, Logic 1 = VL; C

L

= 20 pF.

Parameter

Symbol Min

Typ

Max

Units

RST pin Low Pulse Width

1

-

-

ms

PLL Clock Recovery Sample Rate Range

28

-

216

kHz

Differential RX Mode

Single-Ended RX Mode

-

-

200

475

-

-

ps RMS

ps RMS

XTI Frequency

Crystal

12

-

27.000

MHz

Digital Clock Source

1.024

-

49.152

MHz

XTI Pulse Width High/Low

9

-

-

ns

VL = 3.3 V, 5 V

RMCK/MCLK_OUT Output Frequency

-

-

49.152

MHz

RMCK/MCLK_OUT Output Duty Cycle

45

50

55

%

Slave Mode

ISCLK Frequency

-

-

49.152

MHz

ISCLK High Time

t

sckh

9.2

-

-

ns

ISCLK Low Time

t

sckl

9.2

-

-

ns

OSCLK Frequency

-

-

26.9

MHz

OSCLK High Time

t

sckh

16.7

-

-

ns

OSCLK Low Time

t

sckl

16.7

-

-

ns

I/OLRCK Edge to I/OSCLK Rising Edge

t

lcks

5.7

-

-

ns

I/OSCLK Rising Edge to I/OLRCK Edge

t

lckd

4.2

-

-

ns

OSCLK Falling Edge/OLRCK Edge to SDOUT Output Valid

t

dpd

-

-

15

ns

SDIN/TDM_IN Setup Time Before I/OSCLK Rising Edge

t

ds

3.6

-

-

ns

SDIN/TDM_IN Hold Time After I/OSCLK Rising Edge

t

dh

5.5

-

-

ns

t

lrckh

20

-

-

ns

TDM Mode OLRCK Rising Edge to OSCLK Rising Edge

t

fss

5.3

-

-

ns

TDM Mode OSCLK Rising Edge to OLRCK Falling Edge

t

fsh

4.2

-

-

ns

Master Mode

I/OSCLK Frequency (non-TDM Mode)

48*Fsi/o

-

128*Fsi/o

MHz

I/OLRCK Duty Cycle

49.5

-

50.5

%

I/OSCLK Duty Cycle

45

-

55

%

I/OSCLK Falling Edge to I/OLRCK Edge

t

lcks

-

-

4.2

ns

OSCLK Falling Edge to SDOUT Output Valid

t

dpd

-

-

4.6

ns

SDIN Setup Time Before I/OSCLK Rising Edge

t

ds

2.7

-

-

ns

SDIN Hold Time After I/OSCLK Rising Edge

t

dh

5.5

-

-

ns

TDM Mode OSCLK Frequency

-

-

49.152

MHz