Digital interface specifications, Cs8422 digital interface specifications – Cirrus Logic CS8422 User Manual

Page 16

16

DS692F2

CS8422

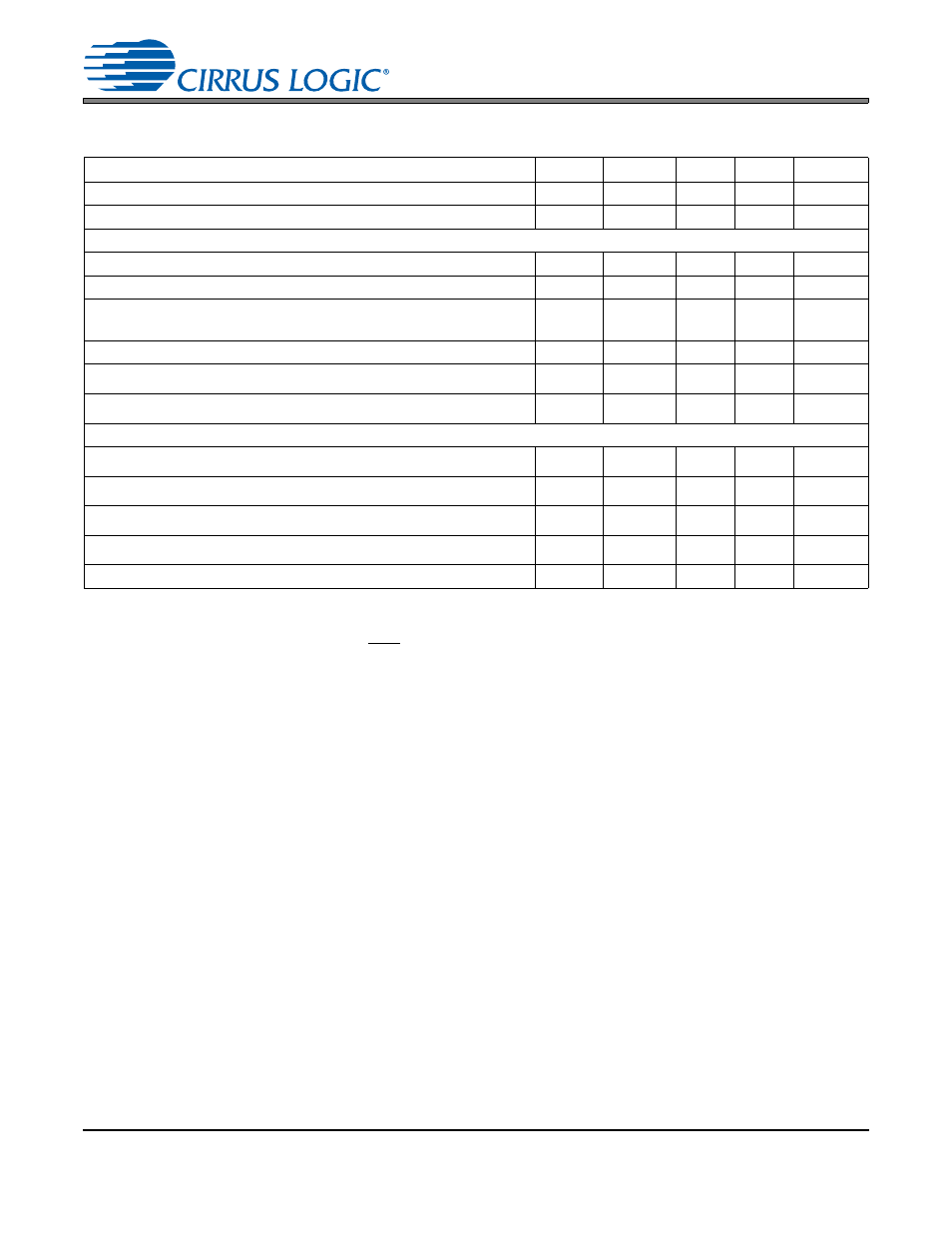

DIGITAL INTERFACE SPECIFICATIONS

AGND = DGND = 0 V; all voltages with respect to 0 V.

Notes:

5.

When a digital signal is sent to the AES RX pins, the pins will draw approximately 730 µA from the digital

signal’s supply from the time RST is released until the RX_MODE, RX_SEL, and INPUT_TYPE bits in

register 03h are properly configured to allow a digital input signal on the driven pins, see

.

6.

Maximum sensitivity in accordance with AES3-2003 section 8.3.3. Measured with eye diagram height

at the specified voltage and width of at least 50% of one-half the biphase symbol period.

Parameter

Symbol

Min

Typ

Max

Units

Input Leakage Current

I

in

-

-

+32

A

Input Capacitance

I

in

-

8

-

pF

Digital Interface Receiver - RXP[1:0], RXN[1:0], RX[3:0]

Differential Input Sensitivity, RXP to RXN

-

-

200

mVpp

Differential Input Impedance, RXP and RXN to GND

-

11

-

k

Single-Ended Input Sensitivity, RX pins, Receiver Input Mode 1

-

-

200

mVpp

Single-Ended Input Impedance, RX pins, Receiver Input Mode 1

-

11

-

k

High-Level Input Voltage, RX pins in Digital mode

V

IH

0.55xVA

-

VA+0.3

V

Low-Level Input Voltage, RX pins in Digital mode

V

IL

-0.3

-

0.8

V

Digital I/O

High-Level Output Voltage (I

OH

= -4 mA)

V

OH

.77xVL

-

-

V

Low-Level Output Voltage (I

OL

= 4 mA)

V

OL

-

-

0.6

V

High-Level Input Voltage

V

IH

0.65xVL

-

-

V

Low-Level Input Voltage

V

IL

-

-

0.3xVL

V

Input Hysteresis

-

0.2

-

V