Note 9), Note 10), Note 11) – Cirrus Logic CS8422 User Manual

Page 19: Note 12), Cs8422

DS692F2

19

CS8422

9.

Typical base band jitter in accordance with AES-12id-2006 section 3.4.2. Measurements are Time In-

terval Error (TIE) taken with 3rd order 100 Hz to 40 kHz band-pass filter. Measured with Sample Rate

= 48 kHz.

10. OLRCK must remain high for at least 1 OSCLK period and at most 255 OSCLK periods in TDM Mode.

11. In TDM formatted master mode, the TDM_IN pin is not supported.

12. In TDM formatted master mode, the OSCLK frequency is fixed at 256*OLRCK.

t

ds

OLRCK

(input)

t

dh

t

sckh

t

sckl

t

fsh

t

fss

OSCLK

(input)

TDM_IN

(input)

SDOUT

(output)

MSB

t

dpd

MSB-1

MSB

MSB-1

t

lrckh

t

ds

MSB

t

dh

t

dpd

MSB-1

I/OLRCK

(input)

I/OSCLK

(input)

SDIN

(input)

SDOUT

(output)

MSB

MSB-1

t

sckh

t

sckl

t

lcks

t

lckd

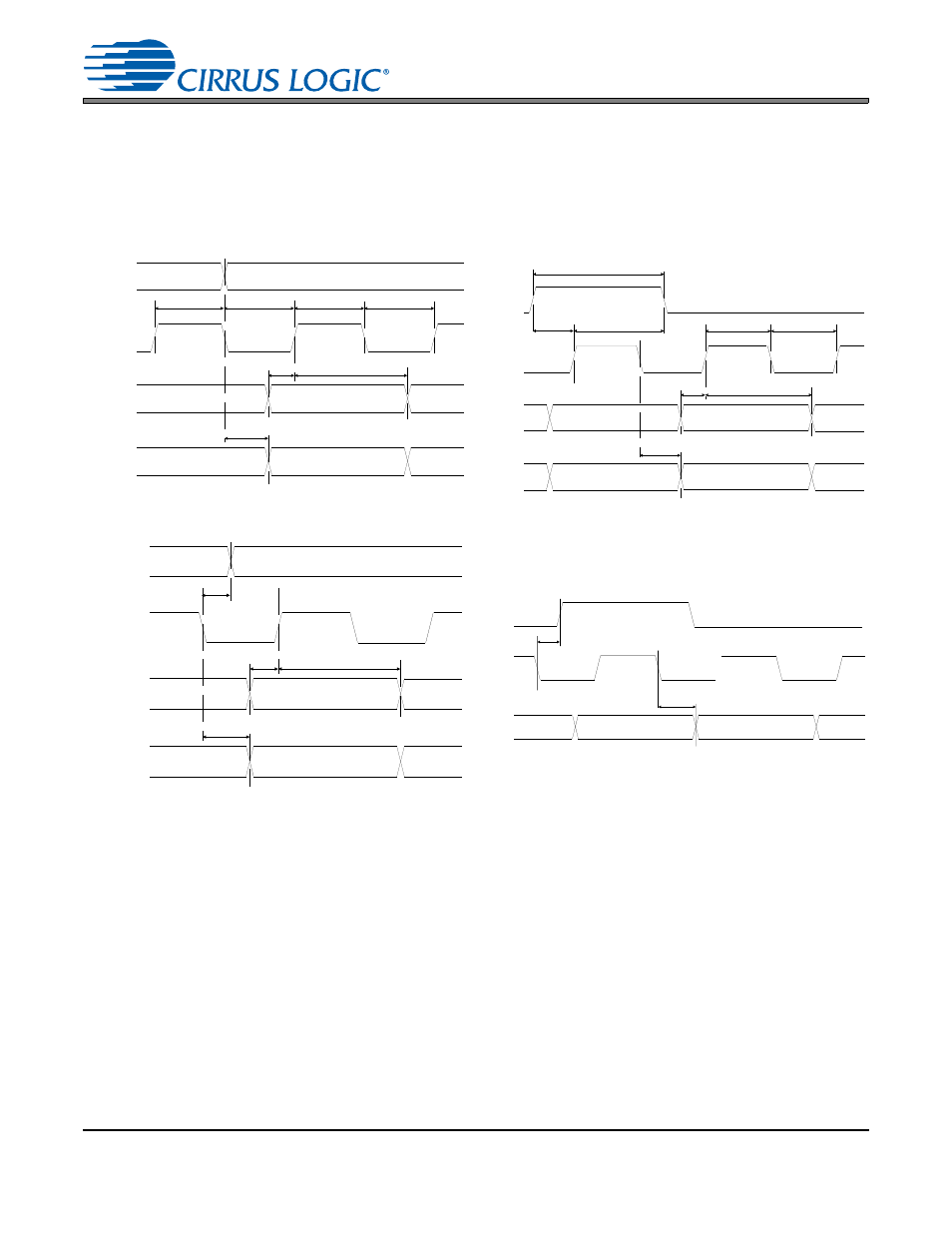

Figure 1. Non-TDM Slave Mode Timing

Figure 2. TDM Slave Mode Timing

OLRCK

(output)

t

dpd

t

fsm

OSCLK

(output)

SDOUT

(output)

MSB

MSB-1

t

ds

MSB

t

dh

t

dpd

MSB-1

t

lcks

I/OLRCK

(output)

I/OSCLK

(output)

SDIN

(input)

SDOUT

(output)

MSB

MSB-1

Figure 3. Non-TDM Master Mode Timing

Figure 4. TDM Master Mode Timing

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1601 (2 pages)

- CS1501 (16 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)