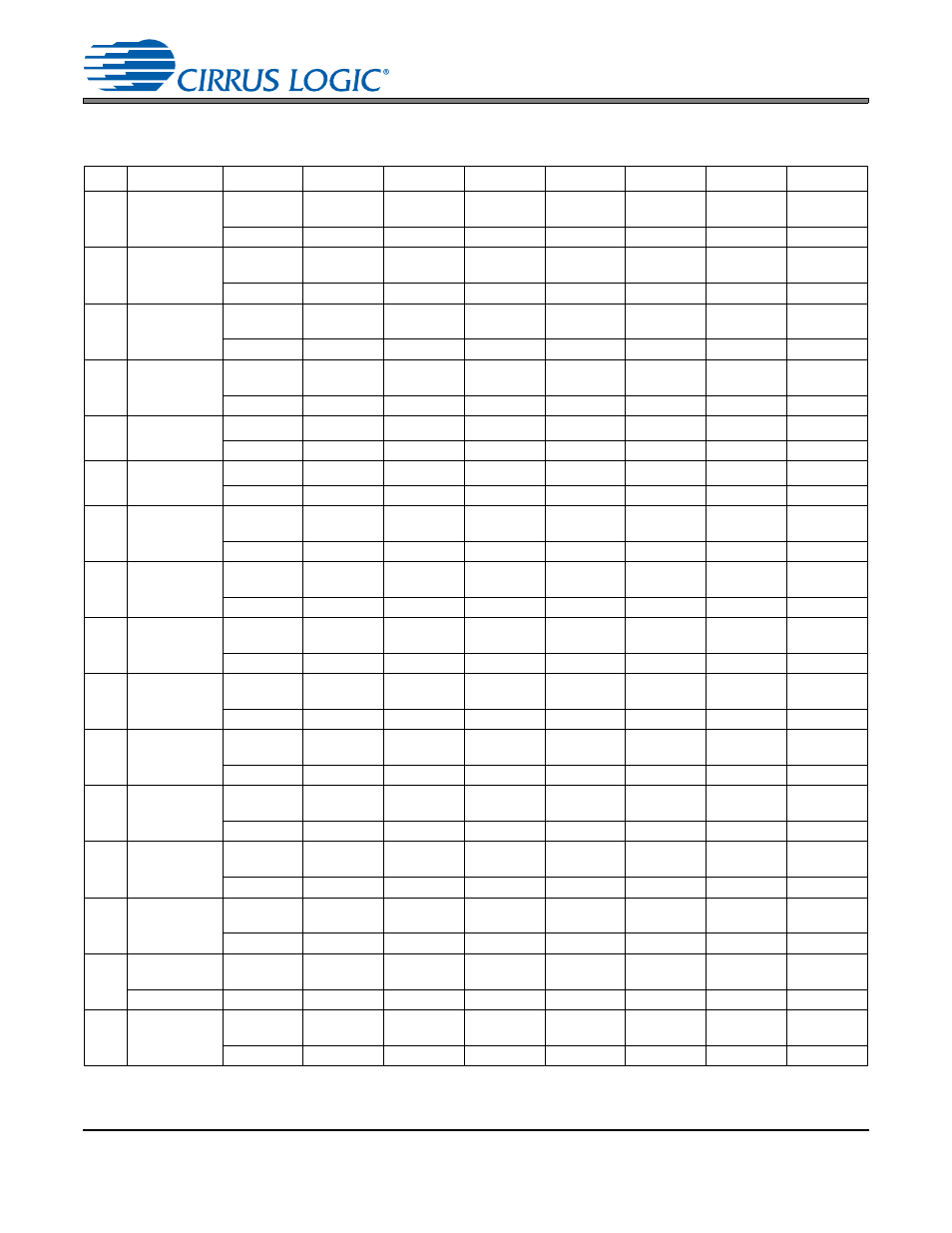

Register quick reference, Table 6. summary of software register bits – Cirrus Logic CS8422 User Manual

Page 45

DS692F2

45

CS8422

10.REGISTER QUICK REFERENCE

This table shows the register names and default values for read-write registers.

Addr

Function

7

6

5

4

3

2

1

0

01h

Chip ID &

Version

ID4

ID3

ID2

ID1

ID0

REV2

REV1

REV0

0

0

0

1

0

0

0

0

02h

Clock Control

PDN

FSWCLK

SWCLK

RMCK_

CTL1

RMCK_

CTL0

INT1

INT0

Reserved

1

0

0

0

0

0

0

0

03h

Receiver Input

Control

RX_MODE

RXSEL1

RXSEL0

TXSEL1

TXSEL0

INPUT_

TYPE

Reserved

Reserved

0

0

0

0

1

0

0

0

04h

Receiver Data

Control

TRUNC

HOLD1

HOLD0

CHS

DETCI

EMPH_

CNTL2

EMPH_

CNTL1

EMPH_

CNTL0

0

0

0

0

0

1

0

0

05h

GPO Control 1

GPO0SEL3

GPO0SEL2

GPO0SEL1

GPO0SEL0

GPO1SEL3

GPO1SEL2

GPO1SEL1

GPO1SEL0

0

0

0

0

0

0

0

0

06h

GPO Control 2

GPO2SEL3

GPO2SEL2

GPO2SEL1

GPO2SEL3

GPO3SEL2

GPO3SEL1

GPO3SEL0

GPO3SEL3

0

0

0

0

0

0

0

0

07h

SAI Clock Con-

trol

SAI_CLK3

SAI_CLK2

SAI_CLK1

SAI_CLK0

SAI_MCLK

Reserved

Reserved

Reserved

0

1

0

0

0

0

0

0

08h

SRC SAO

Clock Control

SAO_CLK3

SAO_CLK2

SAO_CLK1

SAO_CLK0

SAO_

MCLK

SRC_

MCLK1

SRC_

MCLK2

SRC_DIV

0

1

1

0

0

0

0

0

09h

RMCK Cntl.&

Misc.

RMCK3

RMCK2

RMCK1

RMCK0

SRC_

MUTE

Reserved

Reserved

Reserved

0

0

0

0

1

0

0

0

0Ah

Data Routing

Control

SDOUT1_1

SDOUT1_0

SDOUT2_1

SDOUT2_0

MUTE_

SAO1

MUTE_

SAO2

SRCD

Reserved

0

0

0

1

0

0

0

0

0Bh

SAI Data

Format

SIMS

SISF

SIFSEL2

SIFSEL1

SIFSEL0

Reserved

Reserved

Reserved

0

0

0

0

0

0

0

0

0Ch

SAO1 Data For-

mat & TDM

SOMS1

SOSF1

SORES1_1

SORES1_0

SOFSEL1_1 SOFSEL1_0

TDM1

TDM0

0

0

0

0

0

0

0

0

0Dh

SAO2 Data For-

mat

SOMS2

SOSF2

SORES2_1

SORES2_0

SOFSEL2_1 SOFSEL2_0

Reserved

Reserved

0

0

0

0

0

0

0

0

0Eh

RERR Unmask-

ing

Reserved

QCRCM

CCRCM

UNLOCKM

VM

CONFM

BIPM

PARM

0

0

0

0

0

0

0

0

0Fh

Interrupt

Unmasking

PCCHM

OSLIPM

DETCM

CCHM

RERRM

QCHM

FCHM

SRC_

UNLOCKM

0

0

0

0

0

0

0

0

10h

Interrupt Mode

Reserved

Reserved

Reserved

Reserved

RERR1

RERR0

SRC_

UNLOCK1

SRC_

UNLOCK0

0

0

0

0

0

0

0

0

Table 6. Summary of Software Register Bits