5 interrupt handling, Section 7.2.5 “interrupt han, Table 7-13 on – Rainbow Electronics AT86RF231 User Manual

Page 67

67

8111A–AVR–05/08

AT86RF231

or TRAC_STATUS = SUCCESS_DATA_PENDING if the frame pending subfield of the received

ACK frame was set to 1.

7.2.5

Interrupt Handling

The interrupt handling in the Extended Operating Mode is similar to the Basic Operating Mode,

refer to

Section 7.1.3 “Interrupt Handling” on page 38

. The microcontroller enables interrupts by

setting the appropriate bit in register 0x0E (IRQ_MASK).

For RX_AACK and TX_ARET the following interrupts inform about the status of a frame recep-

tion and transmission:

RX_AACK

For RX_AACK it is recommended to enable IRQ_3 (TRX_END). This interrupt is issued only if a

frame passes the frame filtering, refer to

Section 7.2.3.5 “Frame Filtering” on page 61

and has a

valid FCS. This is in contrast to Basic Operating Mode, refer to

Section 7.1.3 “Interrupt Handling”

. The use of the other interrupts is optional.

On reception of a valid PHR an IRQ_2 (RX_START) is issued. IRQ_5 (AMI) indicates address

match, refer to filter rules in

Section 7.2.3.5 “Frame Filtering” on page 61

, and the completion of

a frame reception with a valid FCS is indicated by interrupt IRQ_3 (TRX_END).

Thus, it can happen that an IRQ_2 (RX_START) and/or IRQ_5 (AMI) are issued, but no IRQ_3

(TRX_END) interrupt.

TX_ARET

In TX_ARET interrupt IRQ_3 (TRX_END) is only issued after completing the entire TX_ARET

transaction.

Acknowledgement frames do not issue IRQ_5 (AMI) or IRQ_3 (TRX_END) interrupts.

All other interrupts as described in

Section 6.6 “Interrupt Logic” on page 29

, are also available in

Extended Operating Mode.

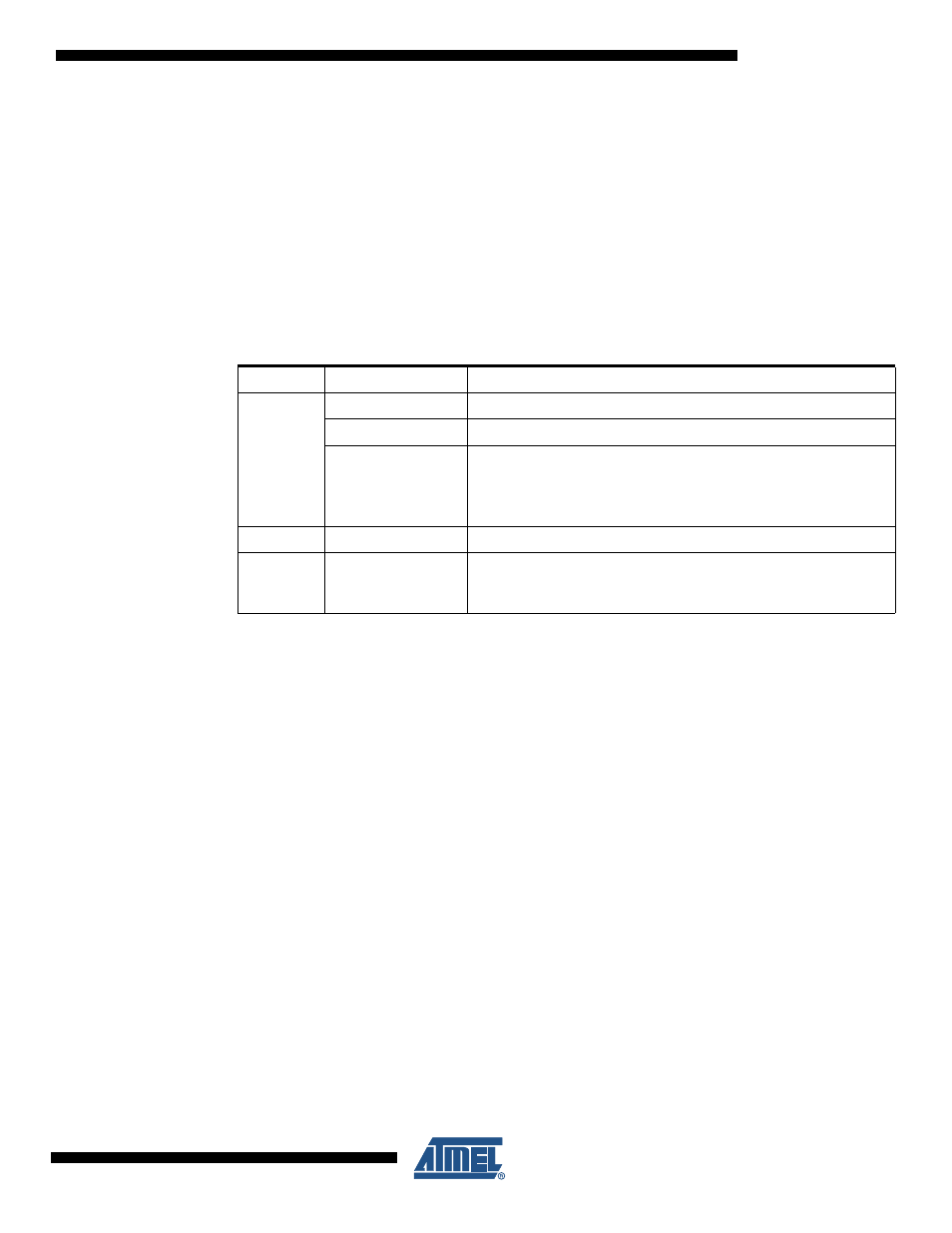

Table 7-13.

Interrupt Handling in Extended Operating Mode

Mode

Interrupt

Description

RX_AACK

IRQ_2 (RX_START)

Indicates a PHR reception

IRQ_5 (AMI)

Issued at address match

IRQ_3 (TRX_END)

Signals completion of RX_AACK transaction if successful

-

A received frame must pass the address filter

-

The FCS is valid

TX_ARET

IRQ_3 (TRX_END)

Signals completion of TX_ARET transaction

Both

IRQ_0 (PLL_LOCK)

Entering RX_AACK_ON or TX_ARET_ON state from

TRX_OFF state, the PLL_LOCK interrupt signals that the

transaction can be started